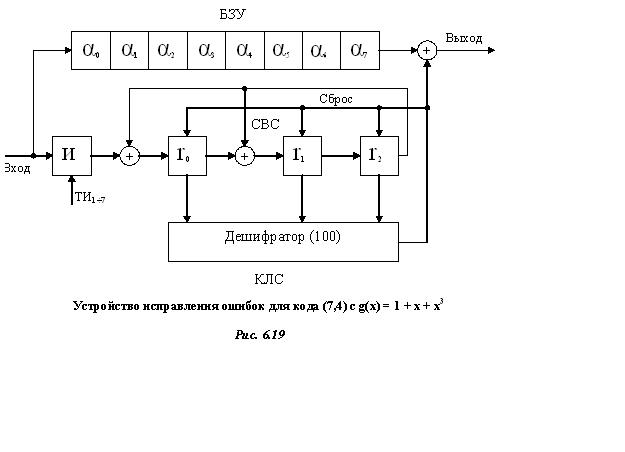

Автоматическое исправление ошибки можно осуществить следующим образом. К разрядам регистра сдвига подключается дешифратор на комбинацию вида 100…0. Выход дешифратора и выход БЗУ подключается ко входам сумматора по модулю 2.

Одновременно со сдвигами в схеме деления после вычисления синдрома осуществляется вывод информации из БЗУ. На (n-i)-м сдвиге на входы сумматора поступят от БЗУ искаженный элемент, а от дешифратора - единица. На выходе сумматора искаженный элемент инвертируется, т.е. ошибка будет исправлена.

Пример 6.19. Рассмотрим

исправление ошибок циклическим (7,4) - кодом с ![]() .

Этот код имеет dmin

= 3, т.е. исправляет все одиночные ошибки. Общий вид схемы

исправления одиночных ошибок для данного кода представлен на рис. 6.19.

.

Этот код имеет dmin

= 3, т.е. исправляет все одиночные ошибки. Общий вид схемы

исправления одиночных ошибок для данного кода представлен на рис. 6.19.

Поясним работу

схемы при исправлении одиночных ошибок на примере. Пусть приемное устройство

зарегистрировало комбинацию 1101101. Данная комбинация поступает в СВС и БЗУ.

После 7-го такта СВС содержит синдром ![]() ,

что свидетельствует о том, что искажен элемент при

,

что свидетельствует о том, что искажен элемент при ![]() (см.

пример 6.15). С 8-го такта комбинация выводится из БЗУ, начиная со старшей

степени. Одновременно в СВС происходят сдвиги синдрома.

(см.

пример 6.15). С 8-го такта комбинация выводится из БЗУ, начиная со старшей

степени. Одновременно в СВС происходят сдвиги синдрома.

Этот процесс представлен в таблице 6.8.

Таблица 6.8

|

№ такта |

Состояние СВС |

Выход БЗУ |

Выход КЛС |

Выход схемы |

||

|

r0 |

r1 |

r2 |

||||

|

7 |

1 |

1 |

0 |

- |

0 |

- |

|

8 |

0 |

1 |

1 |

1 |

0 |

1 |

|

9 |

1 |

1 |

1 |

0 |

0 |

0 |

|

10 |

1 |

0 |

1 |

1 |

0 |

1 |

|

11 |

1 |

0 |

0 |

1 |

1 |

0 |

|

12 |

0 |

0 |

0 |

0 |

0 |

0 |

|

13 |

0 |

0 |

0 |

1 |

0 |

1 |

|

14 |

0 |

0 |

0 |

1 |

0 |

1 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.