В ряде случаев может оказаться целесообразным построение декодирующего устройства на основе схемы для решения рекуррентных соотношений (рис. 6.7).

В этом случае процедура обнаружения ошибок строится следующим образом. По принятым информационным разрядам кодовой комбинации восстанавливаются избыточные элементы принимаемой кодовой комбинации и сравниваются с избыточными элементами, поступающими из канала. Если нет отличия в принимаемых и восстановленных избыточных элементах, то кодовая комбинация считается принятой верно. Если же восстановленные избыточные элементы отличаются от принятых, то фиксируется факт обнаружения ошибки.

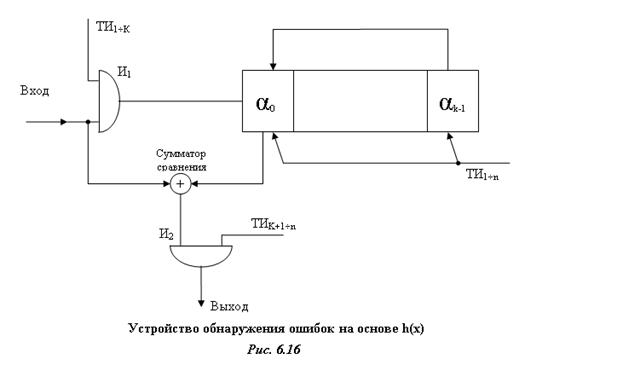

Структурная схема устройства обнаружения ошибок, реализующая описанную процедуру, представлена на рис. 6.16.

Информационные разряды принятой кодовой комбинации циклического (n, k) – кода через схему И1,

открытую на время приема k информационных

элементов, вводятся в регистр из k разрядов.

После приема k-го разряда в схеме происходит

сдвиг информации вправо, и по (k+1)-му такту в

ячейке ![]() оказывается записанным старший

избыточный разряд. Сформированный избыточный разряд поступает из ячейки

оказывается записанным старший

избыточный разряд. Сформированный избыточный разряд поступает из ячейки ![]() на вход сумматора по модулю 2. В то

же самое время со входа схемы на второй вход сумматора поступает старший

избыточный разряд от входа схемы. Начиная с (k+1)-го

такта открывается выход сумматора через схему И2 и

определяется сумма по модулю 2 сравниваемых избыточных символов. “1” на выходе сумматора означает ошибку, “0” – правильный прием. По (k+2)-му

такту в

на вход сумматора по модулю 2. В то

же самое время со входа схемы на второй вход сумматора поступает старший

избыточный разряд от входа схемы. Начиная с (k+1)-го

такта открывается выход сумматора через схему И2 и

определяется сумма по модулю 2 сравниваемых избыточных символов. “1” на выходе сумматора означает ошибку, “0” – правильный прием. По (k+2)-му

такту в ![]() формируется следующий избыточный

символ. Соответствующий избыточный символ в этот же момент поступает от входа

схемы и т.д. Сумматор выдает решение по каждому избыточному разряду. Общее

время работы схемы, необходимое для выявления ошибок в принимаемой комбинации,

не выходит за пределы времени приема комбинации.

формируется следующий избыточный

символ. Соответствующий избыточный символ в этот же момент поступает от входа

схемы и т.д. Сумматор выдает решение по каждому избыточному разряду. Общее

время работы схемы, необходимое для выявления ошибок в принимаемой комбинации,

не выходит за пределы времени приема комбинации.

На рис. 6.17 для сравнения приведены устройства обнаружения ошибок для циклического кода (7,3), построенные по h(x) (Рис 6.17а) и по g(x) (Рис 6.17б)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.