Как и в случае «прямого» вычисления ДПФ,

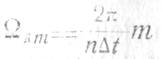

вычисление т-той частотной выборки Gm с помощью БП БПФ эквивалентно определению выходного

напряжения доплеровского фильтра с резонансной частотой  и комплексным коэффициентом

передачи (3.34)

и комплексным коэффициентом

передачи (3.34) ![]() .

Из выражения (3.34) следует, что модуль коэффициента передачи при

совпадении частоты входного сигнала с резонансной частотой эквивалентного

фильтра равен числу «я» точек БПФ. Действительно, на каждом этапе БПф (рис.

3.29) амплитуда сигнала возрастает в два раза, что обеспечивается увеличением

разрядности представления чисел на единицу при суммировании и вычитании в

каждой базовой операции. Если частота входного сигнала не равна резонансной

частоте эквивалентного фильтра, т. е.

.

Из выражения (3.34) следует, что модуль коэффициента передачи при

совпадении частоты входного сигнала с резонансной частотой эквивалентного

фильтра равен числу «я» точек БПФ. Действительно, на каждом этапе БПф (рис.

3.29) амплитуда сигнала возрастает в два раза, что обеспечивается увеличением

разрядности представления чисел на единицу при суммировании и вычитании в

каждой базовой операции. Если частота входного сигнала не равна резонансной

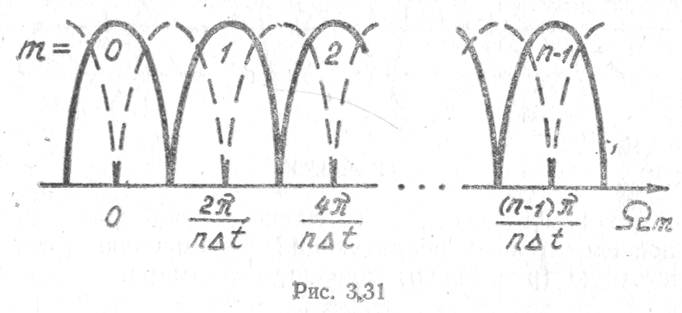

частоте эквивалентного фильтра, т. е. ![]() то имеют место потери в основном за

счет перекрытия АЧХ соседних фильтров (рис. 3.25,а). Одним из способов снижения

этих потерь является выбор числа временных отсчетов вдвое большим необходимого

числа спектральных отсчетов Gm (рис.

3.31, сплошная линия), а

то имеют место потери в основном за

счет перекрытия АЧХ соседних фильтров (рис. 3.25,а). Одним из способов снижения

этих потерь является выбор числа временных отсчетов вдвое большим необходимого

числа спектральных отсчетов Gm (рис.

3.31, сплошная линия), а

также параллельное включение двух наборов

БПФ-фильтров, которые сдвигаются друг относительно друга на половину их поле

полосы пропускания ![]() (рис.

3.31, пунктир). Сдвиг на

(рис.

3.31, пунктир). Сдвиг на ![]() Ω0,64/2 может быть

реализован непосредственно на входе процессор БПФ путем умножения

кодов временных выборок в одном и наборов на exp

Ω0,64/2 может быть

реализован непосредственно на входе процессор БПФ путем умножения

кодов временных выборок в одном и наборов на exp ![]() . Дляповышения быстродействия и уменьшения

ошибок вычислений это умножение обычно совмещается с умножением на множитель Wiна одном из этапов

БПФ.

. Дляповышения быстродействия и уменьшения

ошибок вычислений это умножение обычно совмещается с умножением на множитель Wiна одном из этапов

БПФ.

Для борьбы с боковыми лепестками АЧХ,

как и при выше рассмотренном «прямом» вычислении ДПФ, используется умножение

временных ![]() либо

частотных Gm выборок на соответствующие «окна». Умножение на временное

«окно» также целеесообразно совместить с умножением на Wi, а умножение на частот мое «окно» в схеме ЦСФ (рис. 3.13)

обычно производится путем соответствующей коррекции значений Ксф(f) записанных в ПЗУ Так как использование временных или

частотных оконных функций приводит к ухудшению разрешающей способности по

частоте

либо

частотных Gm выборок на соответствующие «окна». Умножение на временное

«окно» также целеесообразно совместить с умножением на Wi, а умножение на частот мое «окно» в схеме ЦСФ (рис. 3.13)

обычно производится путем соответствующей коррекции значений Ксф(f) записанных в ПЗУ Так как использование временных или

частотных оконных функций приводит к ухудшению разрешающей способности по

частоте ![]() (3.33), то

число точек БПФ увеличивается до значение

(3.33), то

число точек БПФ увеличивается до значение ![]() .

.

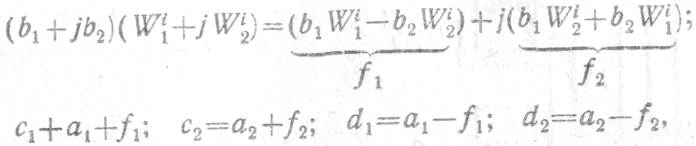

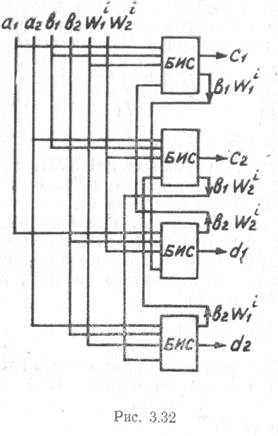

При сравнительно небольших значениях «n» базовая операция (рис. 3.30) может быть выполнена с помощью быстродействующих микропроцессоров (МП), например, серий 1802, 1804. Однако с ростом размера преобразования их быстродействие оказывается недостаточным' (при выполнении 1024-точечного БПФ одним 16-разрядным МП серии 1804 требуется несколько десятков секунд). Поэтому для технической реализации БП БПФ в настоящее время выпускаются специализированные биполярные БИС МП, например, 1815 БФЗ, АЛУ которых содержит два сумматора-вычитателя и умножитель. Так как для получения высокого быстродействия при реализации базовой операции БПФ (рис. 3.30) требуется четыре умножителя, три сумматора и три вычитателя

то в состав БП БПФ входят четыре одинаковых

БИС МП 18it> ВФЗ (рис 3 32) Время выполнения базовой операции ![]() составляет

400 не Еще меньшее время

составляет

400 не Еще меньшее время ![]() ~200 не может быть получено с помощью биполярной БИС МП

1518 ВЖ1. Такие значения

~200 не может быть получено с помощью биполярной БИС МП

1518 ВЖ1. Такие значения ![]() в ряде случаев оказываются достаточными для выполнения

одним БП БПФ цифрового спектрального анализа принимаемых радиолокационных

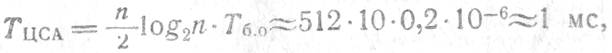

сигналов, так как время такого анализа, например, для 1024-точечного

БПФ равно

в ряде случаев оказываются достаточными для выполнения

одним БП БПФ цифрового спектрального анализа принимаемых радиолокационных

сигналов, так как время такого анализа, например, для 1024-точечного

БПФ равно

что сравнимо с периодом следования зондирующих

импульсов РЛС. Оценим, достаточным ли является такое быстродействие для

реализации ЦСФ в частотной области (рис. 3.13), полагая, что значения его ![]() записаны в ПЗУ:

записаны в ПЗУ:

где ![]() —время, необходимое для выполнения

комплексного умножения двух n-точечных массивов

—время, необходимое для выполнения

комплексного умножения двух n-точечных массивов ![]() .

.

Так как основная доля времени ![]() тратится

на выполнение комплексного умножения

тратится

на выполнение комплексного умножения ![]() , а время выполнения арифметических

операций обычно совмещается с циклами обращения к памяти, то можно

предположить, что

, а время выполнения арифметических

операций обычно совмещается с циклами обращения к памяти, то можно

предположить, что ![]() и

(3.41) приводится к виду

и

(3.41) приводится к виду

![]()

Вычисление ![]() по данной

формуле для 1024-точечного БПФтакже дает результат (~2 мс), приемлемый

для РЛС с механическим сканированием и большой скважностью зондирующих импульсов.

Однако с ростом «n» значения

по данной

формуле для 1024-точечного БПФтакже дает результат (~2 мс), приемлемый

для РЛС с механическим сканированием и большой скважностью зондирующих импульсов.

Однако с ростом «n» значения ![]() также возрастают,

что ограничивает возможности однопроцессорной фильтрации в частотной области не

только для широкополосных сигма лов, но и для простых сигналов, излучаемых с

малым периодом следования либо принимаемых с разных направлений в РЛС с

электрическим сканированием.

также возрастают,

что ограничивает возможности однопроцессорной фильтрации в частотной области не

только для широкополосных сигма лов, но и для простых сигналов, излучаемых с

малым периодом следования либо принимаемых с разных направлений в РЛС с

электрическим сканированием.

Для повышения быстродействия при выполнении

БПФ используют параллелизм вычислений в поточных, итеративных и

матричных процессорах. При построении поточи процессора БПФ учитывается то,

что еще до окончания всех базовых операций на данном этапе можно начинать

вычисления на последующих этапах. Например, из рис. 3.29,6 следует, что

верхнюю базовую операцию на 1-м этапе можно начинать сразу после выполнения

первых трех сверху базовых операции на этапе 0.  Аналогично верхнюю базовую операцию на 2-м этапе можно

выполнять сразу после завершения первых двух сверху базовых операций этапа 1.

Поэтому в состав поточного процессора включают

Аналогично верхнюю базовую операцию на 2-м этапе можно

выполнять сразу после завершения первых двух сверху базовых операций этапа 1.

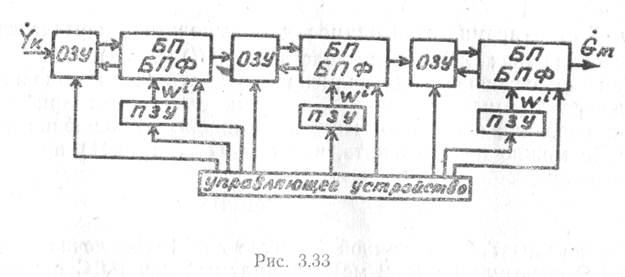

Поэтому в состав поточного процессора включают ![]() одновременно

работающих БП БПФ (в качестве примера на рис. 3.33 представлен поточный

процессор БПФ для п=8). Можно показать [21], что при больших «n» значения

одновременно

работающих БП БПФ (в качестве примера на рис. 3.33 представлен поточный

процессор БПФ для п=8). Можно показать [21], что при больших «n» значения ![]() и

и ![]() у поточного

процессора уменьшаются в log2n раз.

у поточного

процессора уменьшаются в log2n раз.

Итеративный процессор содержит n/2

параллельно работающих БП БПФ,которые одновременно выполняют базовые

операции на каждом из этапов БПФ. Для рис. 3.29 итеративный процессор должен

содержать 4 БП БПФ, например, в виде 16 корпусов БИС МП 1815 ВФЗ. При этом

значения ![]() и

и ![]() составляют

составляют ![]() и

и ![]() соответственно.

соответственно.

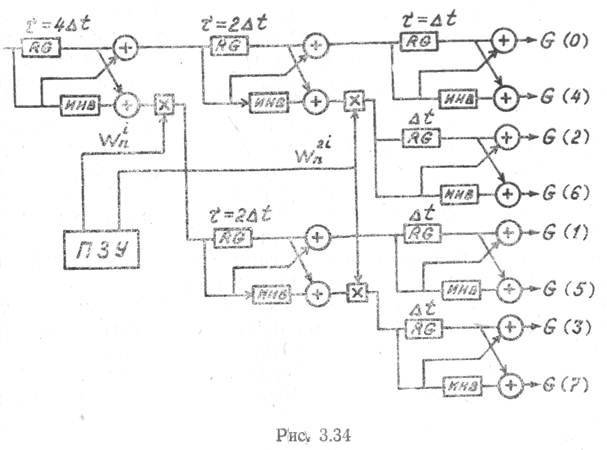

Возможно использование итеративно-поточной структуры процессора БПФ. Упрощенная структурная схема такого процессора для алгоритма БПФ с прореживанием по частоте при п=8 представлена на рис. 3.34. Ввиду последовательной передачи

выборок входного сигнала на вход процессора в его состав наряду с БП БПФ включаются дополнительные устройства памяти в виде межкаскадных регистров сдвига. Количество разрядов в регистрах сдвига соответствует требуемому закону формирования входных массивов на каждом из этапов БПФ (рис. 3.29,6).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.