Такая форма позволяет представить 2L+1 различных чисел (2L отличающихся во абсолютной величине чисел с шагом 2-L). Если результат арифметической операции выходит за верхний предел неравенства (3.29), то происходит переполнение разрядной сетки, приводящее к искажению результата. При согласованной фильтрации такое переполнение может, например, возникнуть, если не будет учтено возможное увеличение в М раз уровня сигнала на выходе фильтра по сравнению с его входным сигналом.

Проблема динамического диапазона практически не возникает при использовании способа с плавающей запятой, так как для ее решения достаточно добавить один-два дополнительных разряда в порядок числа. Однако техническая реализация цифрового фильтра при таком представлении усложняется, а также уменьшается его быстродействие. Причиной этого является необходимость предварительного выравнивания порядков чисел при сложении с последующей нормализацией результата, а при умножении — необходимость выполнения двух операций: перемножения мантис и сложения порядков. Кроме того, при представлении чисел с плавающей запятой будет вноситься ошибка не только при выполнении операций умножения, но и сложения, так как в ходе нормализации часть разрядов одного из чисел теряется.

Учитывая вышеизложенное, особенно более высокое быстродействие, при обработке радиолокационных сигналов шире применяется способ представления чисел с фиксированной запятой, как правило, в дополнительном коде. Разрядность всех матричных умножителей (рис. 3.19) одинакова, при этом число разрядов произведения, как правило, округляется до разрядности представления входного сигнала путем отбрасывания младших разрядов и, при необходимости, добавления единицы в последний разряд. В отличие от умножителей разрядность сумматоров АУ нарастает с увеличением числа регистров по закону log2M. Например, при М = 64 разрядность последнего сумматора АУ должна быть на 6 больше, чем у АЦП.

Произведения, полученные на выходе

арифметических устройств АУ1...АУ4, суммируются с учетом знака в соответствии

с алгоритмом (3.27). Параллельные двоичные коды реальной и мнимой частей

корреляционного интеграла с выходов сумматоров ![]() поступают на устройство вычисления модуля,

называемое иногда «цифровым амплитудным детектором». На практике, как правило,

используются приближенные методы вычисления модуля

поступают на устройство вычисления модуля,

называемое иногда «цифровым амплитудным детектором». На практике, как правило,

используются приближенные методы вычисления модуля ![]() , что связано со сложностью технической

реализации данной операции как на аналоговой, так и на цифровой элементной

базе. Рассмотрим один из приближенных алгоритмов вычисления модуля, называемый

алгоритмом Робертсона. Для этого обозначим R

, что связано со сложностью технической

реализации данной операции как на аналоговой, так и на цифровой элементной

базе. Рассмотрим один из приближенных алгоритмов вычисления модуля, называемый

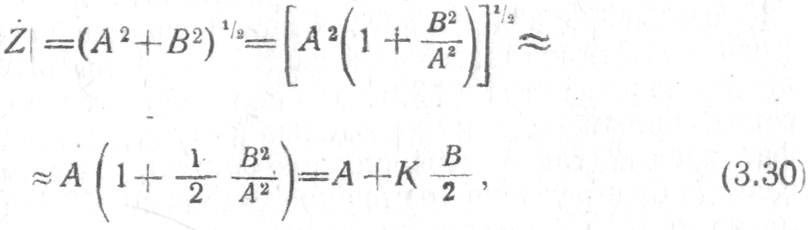

алгоритмом Робертсона. Для этого обозначим R![]() и вначале предположим, что А>В. Тогда по формуле

бинома Ньютона получаем

и вначале предположим, что А>В. Тогда по формуле

бинома Ньютона получаем

где ![]() .

.

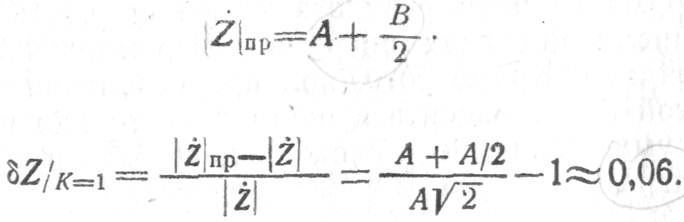

Очевидно, что погрешность данного алгоритма зависит от отношения В/А, а ее максимальное значение будет при В/А = 1. Определим величину максимальной относительной погрешности приближенного вычисления

Итак, максимальная погрешность данного

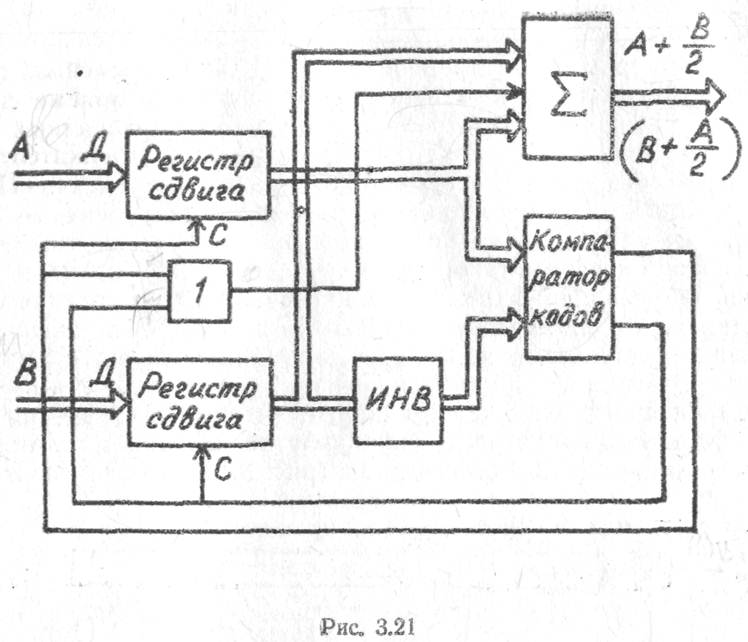

алгоритма составляет около 6%. Заметим, что противоположное предположение В>Адает приближенный алгоритм в виде ![]() . Поэтому схема рис. 3.21, реализующая

данный алгоритм, содержит компаратор кодов, сравнивающий коды реальной и

мнимой части

. Поэтому схема рис. 3.21, реализующая

данный алгоритм, содержит компаратор кодов, сравнивающий коды реальной и

мнимой части ![]() . В зависимости от результата

сравнения компаратор кодов вырабатывает импульс сдвига С, сдвигающий

код реальной либо мнимой части

. В зависимости от результата

сравнения компаратор кодов вырабатывает импульс сдвига С, сдвигающий

код реальной либо мнимой части ![]() на один разряд вправо в

соответствующем регистре сдвига, после чего параллельный сумматор реализует

операцию приближенного алгоритма.

на один разряд вправо в

соответствующем регистре сдвига, после чего параллельный сумматор реализует

операцию приближенного алгоритма.

Иногда для дальнейшего упрощения алгоритма

вычисления ![]() производят

отбор максимального значения кода

производят

отбор максимального значения кода ![]() , что приводит к

потерям в пороговом сигнале, не превышающем 0,7 дБ [10].

, что приводит к

потерям в пороговом сигнале, не превышающем 0,7 дБ [10].

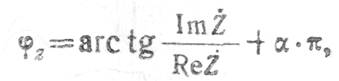

В ряде случаев наряду с вычислением ![]() при цифровой обработке

сигналов необходимо произвести вычисление фазы корреляционной суммы

при цифровой обработке

сигналов необходимо произвести вычисление фазы корреляционной суммы

где

Использование для вычисления ![]() простых аппроксимирующих

выражений функции «arc tg» недопустимо ввиду больших ошибок аппроксимации. Поэтому

одним из способов технической реализации вычислителя

простых аппроксимирующих

выражений функции «arc tg» недопустимо ввиду больших ошибок аппроксимации. Поэтому

одним из способов технической реализации вычислителя ![]() является применение ПЗУ, в ячейках памяти

которого хранятся все возможные значения

является применение ПЗУ, в ячейках памяти

которого хранятся все возможные значения ![]() от 0° до 90°. Требуемая дискретность

значений qiz обеспечивается

выбором микросхемы ПЗУ с достаточными объемом памяти и разрядностью хранимых в

памяти чисел. Адресами ПЗУ являются цифровые коды значений

от 0° до 90°. Требуемая дискретность

значений qiz обеспечивается

выбором микросхемы ПЗУ с достаточными объемом памяти и разрядностью хранимых в

памяти чисел. Адресами ПЗУ являются цифровые коды значений ![]() . Данная

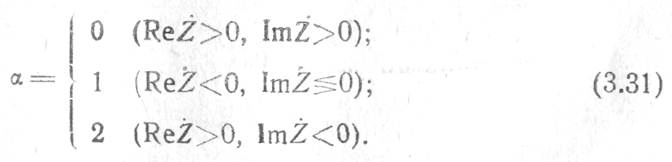

схема должна быть дополнена схемой вычисления а в соответствии с алгоритмом

(3.31). Необходимо отметить, что подобный метод с использованием ПЗУ может быть

применен и для нахождения

. Данная

схема должна быть дополнена схемой вычисления а в соответствии с алгоритмом

(3.31). Необходимо отметить, что подобный метод с использованием ПЗУ может быть

применен и для нахождения ![]() .

.

Недостатком рассмотренной схемы ЦСФ во

временной области (рис. 3.19) является ее сложность, особенно при приеме

сигналов с большой, когда требуемое число многоразрядных регистров,

сумматоров, и самое главное, матричных умножителей равное ![]() составляет сотни и даже тысячи.

Поэтом на практике иногда находят применение нерекурсивные ЦСФ бинарным

квантованием комплексной амплитуды входного сигнала. Отличием схемы такого

фильтра от рис. 3.19 является применение одноразрядных регистров и переход от

умножения в соответствии с (3.27) параллельных кодов в МУ к суммированию тех

значений импульсной характеристики, для которых имеется единичная выборка принимаемого

сигнала.

составляет сотни и даже тысячи.

Поэтом на практике иногда находят применение нерекурсивные ЦСФ бинарным

квантованием комплексной амплитуды входного сигнала. Отличием схемы такого

фильтра от рис. 3.19 является применение одноразрядных регистров и переход от

умножения в соответствии с (3.27) параллельных кодов в МУ к суммированию тех

значений импульсной характеристики, для которых имеется единичная выборка принимаемого

сигнала.

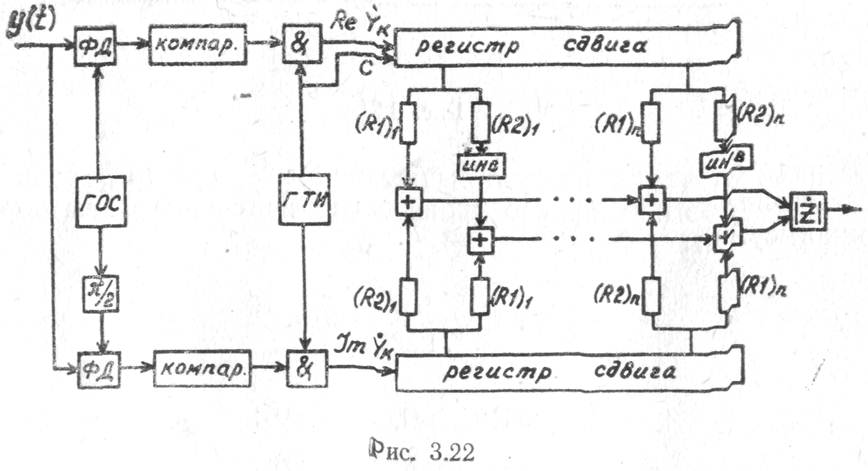

Дальнейшим упрощением является аналого-цифровая схема согласованного фильтра с бинарным квантованием комплексной амплитуды принимаемого сигнала (рис. 3.22). После фазового детектирования

принимаемого сигнала в двух квадратурных

подканалах с помощью генераторов гармонических опорных сигналов ГОС,

амплитудного квантования на два уровня (0,1) в компараторе и временной

дискретизации в схеме совпадения с тактовой частотой генератора тактовых

импульсов ГТИ временные выборки ![]() , заполняют разряды соответствующих регистров сдвига.

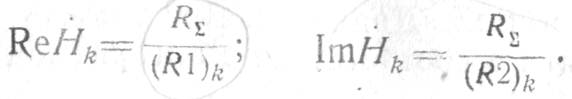

Умножение временных выборок на комплексную импульсную характеристику

согласованного фильтра (3.27) осуществляется путем деления выходных напряжений

триггеров регистров сдвига в делителях, состоящих из прецизионных резисторов

, заполняют разряды соответствующих регистров сдвига.

Умножение временных выборок на комплексную импульсную характеристику

согласованного фильтра (3.27) осуществляется путем деления выходных напряжений

триггеров регистров сдвига в делителях, состоящих из прецизионных резисторов

![]()

![]() и входных сопротивлений

и входных сопротивлений ![]() сумматоров

сумматоров

Например, для согласованной фильтрации

простого радиоимпульса с доплеровской частотой ![]() .

.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.