(рис. 3.26,6 сплошная линия, пунктиром показана исходная АЧХ вида sinxlx). Из данного рисунка следует, что ценой ухудшения разрешающей способности по частоте (расширение главного максимума АЧХ) применение временного «окна» позволило повысить прямоугольность АЧХ эквивалентных фильтров и снизить уровень ее боковых лепестков. Так, например, для времен-* кого «окна», описываемого функцией Кайзера-Бесселя [11], уровень боковых лепестков АЧХ достигает — 82 дБ при расширении ее главного максимума на уровне — 3 дБ примерно в 2 раза. Максимальные потери при вычислении взвешенного ДПФ не превышают 3...4 дБ [12].

Учитывая эквивалентность операций умножения

функций во временной области свертке спектров этих функций в частотной области,

весовую обработку можно также реализовать взвешенным суммированием соседних

спектральных отсчетов на выходе вычислителя ДПФ (частотное «окно»). Значения

весовых коэффициентов ![]() как для временного, так и для частотного

«окна» представляются с высокой точностью в виде многоразрядного

двоичного кода.

как для временного, так и для частотного

«окна» представляются с высокой точностью в виде многоразрядного

двоичного кода.

Структурная схема устройства взвешенного ДПФ

(3.35) для одной частотной выборки может быть представлена в виде рис. 3.19,

где ![]() Операции

умножения на

Операции

умножения на ![]() могут

производиться не только в МУ (рис. 3.20), но и при наличии времени (например,

в случае доплеровской фильтрации — рис. 3.24) с помощью арифметико-логических

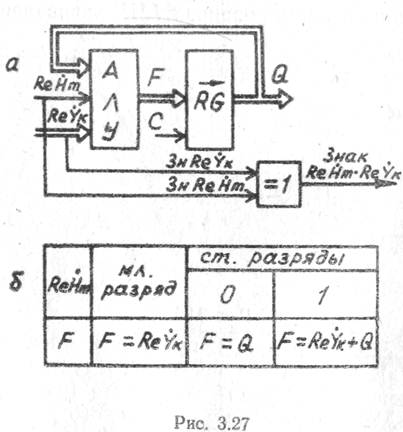

устройств (АЛУ, рис. ^.27). Значения Re

могут

производиться не только в МУ (рис. 3.20), но и при наличии времени (например,

в случае доплеровской фильтрации — рис. 3.24) с помощью арифметико-логических

устройств (АЛУ, рис. ^.27). Значения Re![]() поступают на вход АЛУ в виде

последовательного двоичного кода младшими разрядами вперед, а значения Re

поступают на вход АЛУ в виде

последовательного двоичного кода младшими разрядами вперед, а значения Re![]() в виде параллельного двоичного

кода. АЛУ в зависимости от кода множителя Re

в виде параллельного двоичного

кода. АЛУ в зависимости от кода множителя Re![]() может работать в трех режимах (рис. 3.27,6). Учитывая, что

может работать в трех режимах (рис. 3.27,6). Учитывая, что ![]() , целесообразно

разрядность представления произведения ограничить равной разрядности множимого

, целесообразно

разрядность представления произведения ограничить равной разрядности множимого

![]() ,

,

отбрасывая в регистре младшие разряды путем подачи на него импульсов сдвига С после образования каждой промежуточной суммы. Знак произведения определяется с помощью схемы «исключающее ИЛИ».

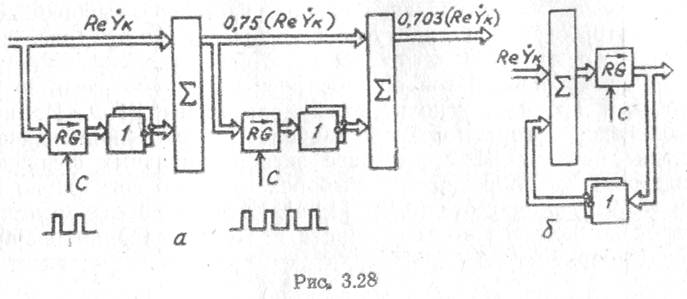

Другим способом последовательно-параллельного умножения может быть схема, реализующая итерационный алгоритм (рис. 3.28).

В состав схемы (рис. 3.28,а) входят ряд последовательно включенных комбинационных сумматоров, осуществляющих суммирование прямого кода 1-го слагаемого с обратным кодом частного от деления 1-го слагаемого на 2l, где l — число импульсов сдвига на регистрах, установленных на вторых входах сумматоров. При необходимости получения высокой точности вычисления множителя схема получается громоздкой, поэтому ее часто заменяют схемой рис. 3.28,6.

Рассмотрим требования, предъявляемые к блокам вычислителя ДПФ (рис, 3.23), Объем памяти входных ОЗУ оценивается по формуле

где ![]() — количество выборок с одной дальности;

— количество выборок с одной дальности;

![]() —количество

дискрет дальности.

—количество

дискрет дальности.

В случае, когда ![]() =п (числу точек ДПФ), последняя формула

принимает вид

=п (числу точек ДПФ), последняя формула

принимает вид

где ![]() —максимальное время задержки

обнаруживаемого

—максимальное время задержки

обнаруживаемого

сигнала;

![]() — требуемые разрешающие способности

цифрового приемного устройства по частоте и времени запаздывания соответственно;

— требуемые разрешающие способности

цифрового приемного устройства по частоте и времени запаздывания соответственно;

![]() — коэффициент, учитывающий расширение

полосы пропускания эквивалентного фильтра-ДПФ за счет весовой обработки

входной последовательности во временном «окне», например, для функции

(3.36)

— коэффициент, учитывающий расширение

полосы пропускания эквивалентного фильтра-ДПФ за счет весовой обработки

входной последовательности во временном «окне», например, для функции

(3.36) ![]() =1,21.

=1,21.

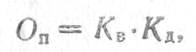

Число разрядов представления чисел пр определяется динамическим диапазоном изменения входных сигналов плюс знаковый разряд

где ![]() дБ — коэффициент, учитывающий флуктуации

амплитуды сигнала за счет изменения условий распространения радиоволн;

дБ — коэффициент, учитывающий флуктуации

амплитуды сигнала за счет изменения условий распространения радиоволн;

Kper — коэффициент регулирования системы АРУ.

Учитывая реальные значения Dвх ![]() 100 дБ для радиолокационных

приемников, а также значения

100 дБ для радиолокационных

приемников, а также значения ![]() радиолокационных сигналов в

соотношении (3.28), справедливом и для ДПФ, делаем вывод, что вычисление каждой

частотной выборки ДПФможет потребовать миллиардного быстродействия АУ

(рис. 3.23), работающего в 16-разрядной сетке. Поэтому в случае приема сигналов

с большой базой при построении ЦСФ в частотной области, как правило,

используются алгоритмы БПФ. Из всего многообразия алгоритмов БПФ

наиболее широкое применение на практике находит БПФ в базисе экспоненциальных

функций с использованием прореживания выборок входного сигнала по времени

(3.39) и по частоте (3.40) [1,20]. Если число «n» временных выборок не является степенью числа 2, то оно

дополняется нулевыми выборками

радиолокационных сигналов в

соотношении (3.28), справедливом и для ДПФ, делаем вывод, что вычисление каждой

частотной выборки ДПФможет потребовать миллиардного быстродействия АУ

(рис. 3.23), работающего в 16-разрядной сетке. Поэтому в случае приема сигналов

с большой базой при построении ЦСФ в частотной области, как правило,

используются алгоритмы БПФ. Из всего многообразия алгоритмов БПФ

наиболее широкое применение на практике находит БПФ в базисе экспоненциальных

функций с использованием прореживания выборок входного сигнала по времени

(3.39) и по частоте (3.40) [1,20]. Если число «n» временных выборок не является степенью числа 2, то оно

дополняется нулевыми выборками

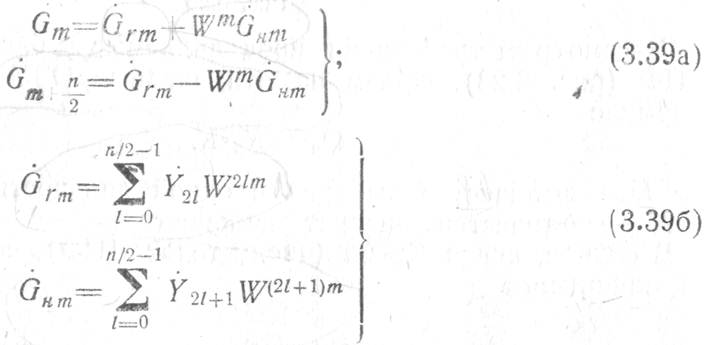

где m=0,1,2,…, n;

где т=0, 1, 2.....п 2—1.

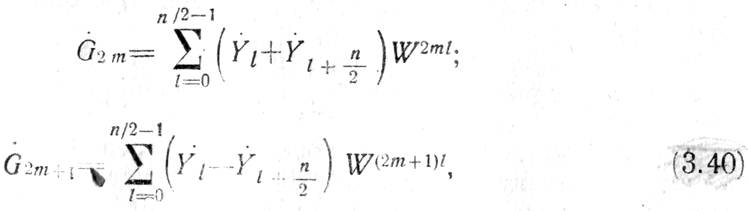

В качестве примера на рис. 3.29,а и б представлены направленные графы вычисления 8-точечного БПФ для алгоритмов с прореживанием по времени и по частоте соответственно. Кружками обозначены сумматоры комплексных чисел, а стрелками вдоль соединительных линий — умножители комплексных чисел на множитель, указанный возле стрелки.

Общая структурная схема вычислителя

(процессора) БПФ сохраняется такой же, как и у вычислителя ДПФ (рис. 3.23),

однако построение его АУ значительно упрощается ввиду уменьшения

необходимого числа умножителей комплексных чисел в  раз [1]. Так как на всех этапах БПФ

(рис. 3.29,а, б) выполняется одна и та же базовая операция, то

структурные схемы АУ в

раз [1]. Так как на всех этапах БПФ

(рис. 3.29,а, б) выполняется одна и та же базовая операция, то

структурные схемы АУ в

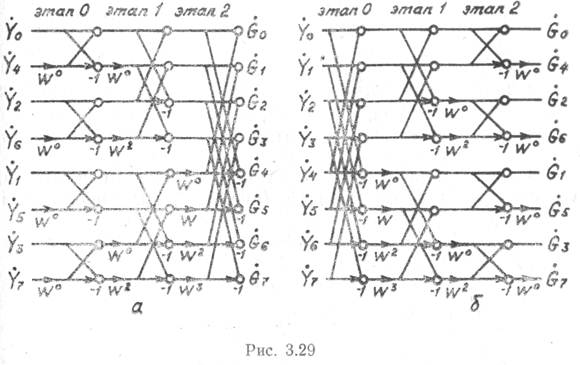

обоих случаях могут содержать лишь один базовый процессор (БП), последовательно реализующий временную (рис. 3.30.а) либо частотную (рис. 3.30,6) «бабочку» Адамара.

Входными операндами ![]() такого процессора являются комплексные

числа, соответствующие квадратурным составляющим выборок входного сигнала или

результатам, полученным на каждом из этапов БПФ. Эти результаты помещаются,

как правило, в освобождающиеся ячейки входного ОЗУ. В соответствии с рис. 3.30

БП БПФ может быть реализован на сумматорах многоразрядных кодов с параллельным

переносом, инверторах на логических элементах и матричных умножителях.

такого процессора являются комплексные

числа, соответствующие квадратурным составляющим выборок входного сигнала или

результатам, полученным на каждом из этапов БПФ. Эти результаты помещаются,

как правило, в освобождающиеся ячейки входного ОЗУ. В соответствии с рис. 3.30

БП БПФ может быть реализован на сумматорах многоразрядных кодов с параллельным

переносом, инверторах на логических элементах и матричных умножителях.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.