1.Design Entry & Management

Creating HDL Text Modules

Course 1

1. Bottom-Up Design Concepts

• Start by creating a new workspace and design

• Use the New Source File Wizards

• Add existing files

• Create an empty design

• Complete the source code

• Check syntax for errors

• Verify the functionality of the design

• Create a top-level diagram or entity

1.1 Creating Bottom-Up Design

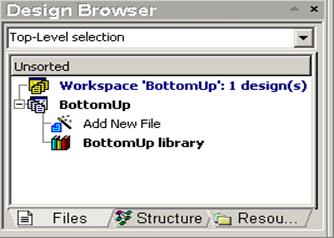

• First, create a new workspace (File | New Workspace). You will be asked to specify its name. To set up a new design, you can also select the Design option in the File| New menu.

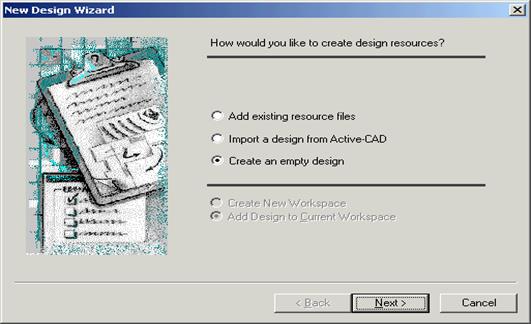

• In the New Design Wizard window, you can choose the design entry method:

– To add existing files, check the Add existing resource files option. Select the source files in the Open window and finish the design creation by clicking the Finish button.

– To import a design from Active-CAD, check the Import a design from Active-CAD option.

– To create an empty design, check the Create an empty design option.

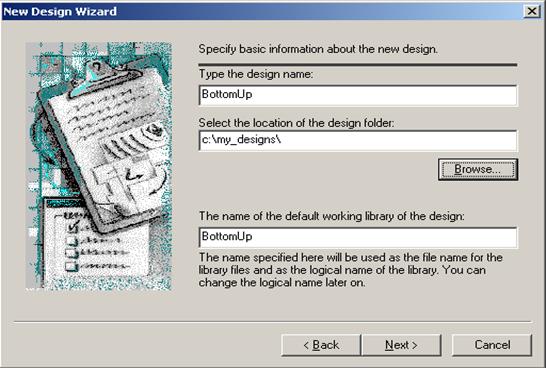

• Type the name of the design, for example BottomUp and click the Next button.

See 1.1 ref. A for more details

1.1 Ref. A The Design Wizards

The Design Wizard simplifies the

process that guides you through initial stages of design development.

By using the Design Wizard, you will create a new design.

• Check the Create an empty design option and click Next.

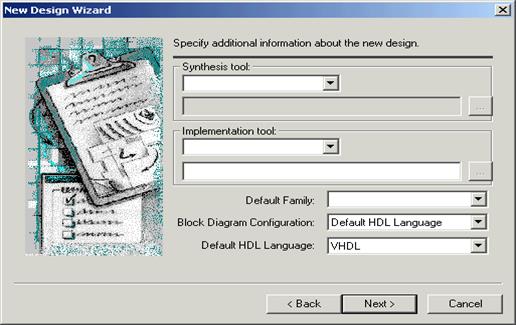

• In the window, you can specify information on:

• Configuration of Block Diagram Editor

• Default language: VHDL or Verilog.

• Synthesis and implementation tools

• Default target device family

•

• 1.1 Ref. C The Design Wizards

• In the next window, you can set:

• Design name,

• Location of the design folder,

• Name of the default working library.

•

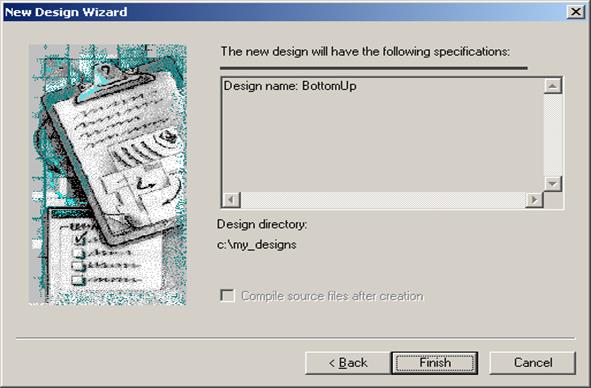

• 1.1 Ref. D The Design Wizards

• In the last window of the New Design Wizard, press the Finish button to accomplish the design creation stage.

•

•

•

• 1.2 Creating Bottom-Up Design

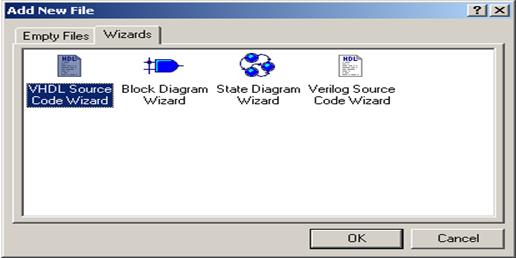

• Double-click the Add new file icon. The Add New File dialog opens.

• Click Wizards and select the VHDL Source Code Wizard.

•

• See 1.3 ref.B for more details

• Click OK to start the New VHDL Source Code Wizard.

• 1.3 Creating Bottom-Up Design

• Check Add the generated file to the design option and advance by clicking the Next button. Type the name of the file: counter. You can also use the Browse button to add an existing file at this stage.

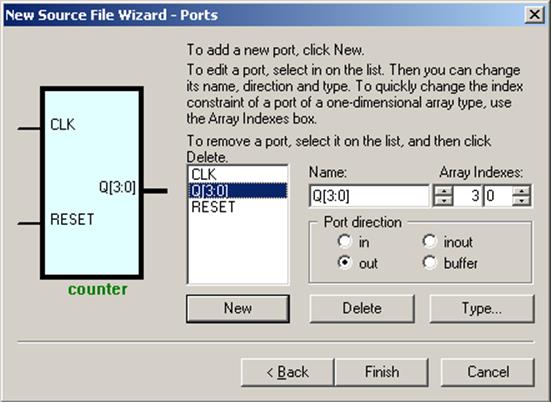

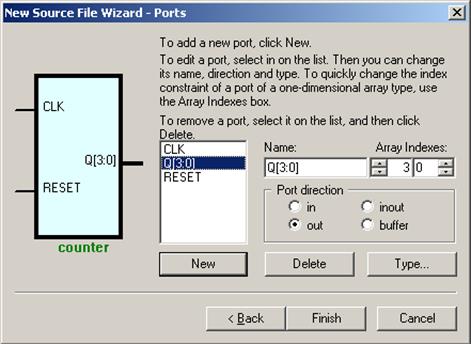

• Define the following ports:

• Input Ports:

• - CLK

• - RESET

• Output Port:

• - Q [3:0]

•

Click the Finish

button.

•

1.3 Ref. B Design Wizard - Ports

• To add a port, click the New button and type the name of a port.

• To change a port type, click the appropriate button in the Port direction box. There are four types:

– In

– Out

– Inout

– Buffer

• To remove any port, click

its name on the list and click

the Delete button.

•

To create a bus, add a new

port name and click the

Array Indexes arrows to

specify the bus width.

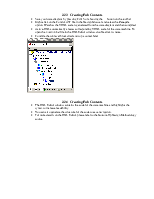

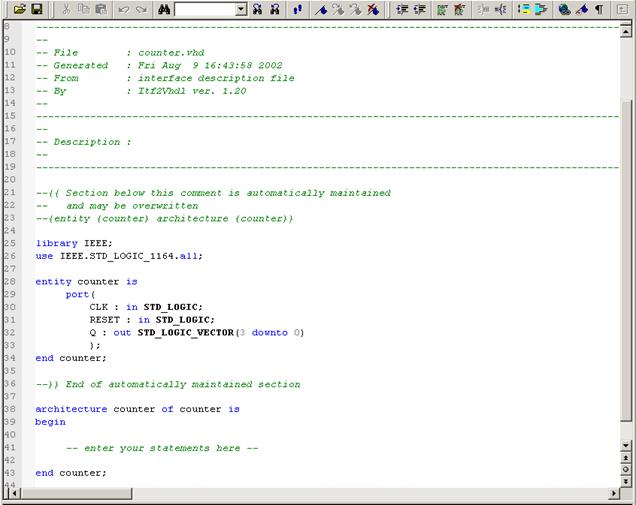

1.4 Creating Bottom-Up Design

•

HDL Editor window

contains the skeleton

of the counter.

•

Click the icon to open the Language

Assistant window.

• Open the Tutorial branch and select the Counter template.

• Drag the Counter template to the HDL Editor window and drop it after the: --Enter your statements here line.

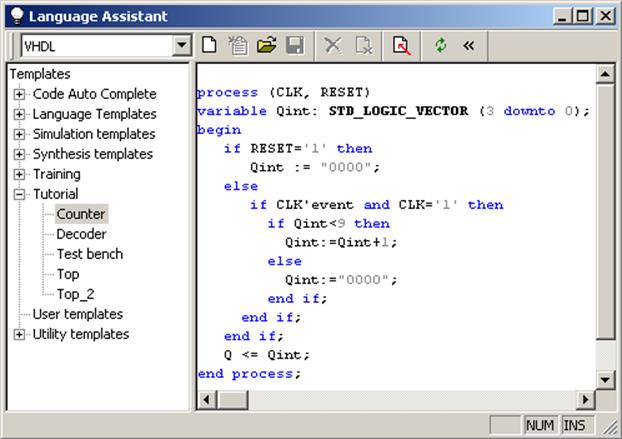

1.4 Ref. A Language Assistant

• The Language Assistant window contains the templates of frequently used models, user-defined models, and VHDL or Verilog constructs.

• You can drag the templates to the HDL Editor window or select the Use option from the pop-up menu.

• You can also take advantage of the Auto-Complete option

Type the first couple of letters of the VHDL or Verilog keyword and it will be automatically completed. You can now press the Right Arrow or Space key on the keyboard to complete the word or press the Ctrl+Enter keys to insert a language template.

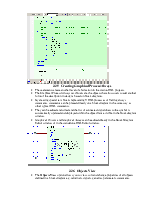

1.5 Creating Bottom-Up Design

The HDL Editor offers ways to efficiently manage the code by performing the following operations:

• Enables keyword coloring for VHDL, Verilog, and C/C++/Handel-C

• Increases indentation of selected blocks

• Comments selected part of code

• Creates groups out of highlighted blocks

• Automatically creates the structure for the source code

• Auto-formats the source code

• Sets bookmarks in the code for easy navigation

• Highlights incorrect constructs after compilation

• Finds and replaces given strings

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.