• The SWIFTTM SmartModels Library is an external library containing the behavioral simulation models of the standard integrated circuits.

• The range and complexity of models varies and starts from simple TTL devices, such as gates, and ends with complex VLSI structures, such as microprocessors and high-density programmable logic.

• Active-HDL provides an interface that allows customers to use these models within the Active-HDL environment

• The SmartModels Library's software (swift.dll) is required to use SmartModels in Active-HDL

• The inclusion of SmartModels Libraries allows users to target Virtex-II Pro devices as well (fully supports PowerPC and Rocket I/O)

12.3a SWIFT & Active-HDL

Sample Design

• Install SmartModel library ‘i27256’

• Open SwiftModel design

• Open runme.do macro and execute it

We are going to simulate model “i27256” in Active-HDL …

12.3b SWIFT Sample Design

Creating foreign architecture

• To use SmartModels in Active-HDL's VHDL-based designs, the communication between an external library and the Active-HDL environment has to be established.

• It can be done by using the library's interface (swift.dll).

• Additionally, Active-HDL provides a program that allows users to create a code containing the foreign entity/architecture pair associated with the SmartModels library.

• Then, such a code can be compiled and used in your design. Active-HDL's sm_prepare creates entity/foreign architecture pairs for SmartModels automatically.

12.3c SWIFT Sample Design

Compilation & Simulation

12.3d SWIFT & Active-HDL

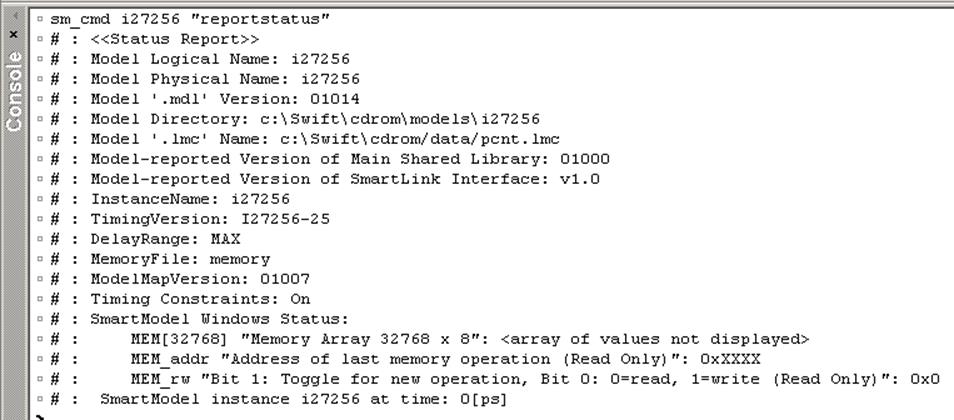

Command Channel

• The command channel is a SmartModel feature that allows the user to invoke SmartModel specific commands.

• The interface built-in to the Active-HDL environment allows customers to use two kinds of commands : Model Commands & Session Commands

Active-HDL Interfaces

Simulink® Interface

Course 13

Overview

The MathWorks' MATLAB®/Simulink® simulation environment provides a powerful

high level mathematical modeling environment for DSP systems that can be widely

used for algorithm development and verification.

Active-HDL provides an interface to MATLAB ver. 6.5 and Simulink ver. 5.0

simulation environment, which allows co-simulation of functional blocks described by

using mathematical formulas and behavioral models described by using hardware

description languages.

The Simulink Interface provides users with the following benefits:

• Intuitive interface that fills the gap between HDL simulation and high level mathematical modeling environment for DSP systems

• Displaying simulation results in both the Simulink environment and the Active-HDL waveform window

• Automatic value conversion between Active-HDL and Simulink

• Advanced testbenches employing complex mathematical formulas used to stimulate unit under test

• Integration with Xilinx System Generator™

13.1 Using Co-Simulation Wizard for Simulink

The interface delivered with the Active-HDL installation program allows you to select

a module or entity that will be used as a black-box during the verification process

performed within Simulink.

It can be used in both VHDL and Verilog designs and interfaces to the MATLAB

environment.

Before co-simulation is initialized and performed by Simulink and Active-HDL,

you need to specify additional configuration settings and a working library that can

be generated by the Co-Simulation Wizard for Simulink.

13.2 Using Co-Simulation Wizard for Simulink

- units for co-simulation

To start the co-simulation process in MATLAB environment, first you need to create

a library for Simulink and then select units to be co-simulated.

This step can be done by using the Co-Simulation Wizard for Simulink.

To run the Co-Simulation Wizard for Simulink in Active-HDL:

1. Open the Active-HDL design that contains units to be co-simulated and compile sources.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.