VHPI/PLI wizard is available in Tools menu. This wizard creates templates for PLI applications.The VHPI/PLI wizard also generates makefiles for GCC compiler for windows (installed with Active-HDL) or Visual C++ compiler.

D.2 How to use Verilog PLI

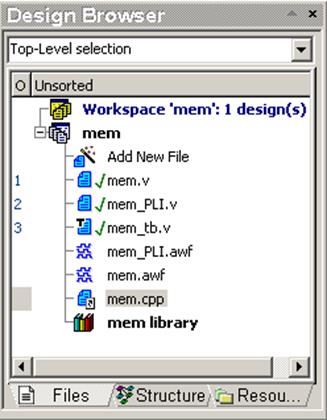

• Open mem design

There are three source files:

• mem.v – behavioral memory

• mem_PLI.v – the same memory but described with use of PLI

• mem_tb.v – Testbench for both memories

D.3 How to use Verilog PLI

• Open the mem_PLI.v file

there are two non-standard tasks called: $write_mem, $read_mem

These tasks are described in C language with use of PLI Interface

module ram (WE, DATA, Q, ADDR);

parameter word_size = 8;

parameter addr_size = 16;

//parameter mem_size = 65536;

output [(word_size-1):0] Q;

reg [(word_size-1):0] Q;

input [(word_size-1):0] DATA;

input [(addr_size-1):0] ADDR;

input WE;

always @(WE or ADDR or DATA) if (WE) $write_mem(ADDR, DATA);

always @(WE or ADDR or DATA) Q = $read_mem(ADDR);

endmodule

D.4 How to use Verilog PLI

• Open the mem.cpp file

There is source code in C language for both tasks: $write_mem, $read_mem

The interface with Active-HDL is made with use of veriusertfs

structure.

s_tfcell veriusertfs[] =

• {

• {userfunction, 0, Check_Read_mem, Size_Read_mem, Read_mem, 0, "$read_mem"},

• //$read_mem(address);

• {usertask, 0, Check_Write_mem, 0, Write_mem, 0, "$write_mem"},

• //$write_mem(address, data);

• {0} /*** final entry must be 0 ***/

• };

•

• This file should be compiled by a C/C++

compiler to generate a DLL file.

In this example the DLL file has already been created for you

D.5 How to use Verilog PLI

Now you have to attach DLL file to Active-HDL simulator

• Open the Settings window from the Design menu

Answer NO, if requested to compile files

• Select the Verilog PLI tab

• Press the Add new application button

• Find the memory.dll file

it is located in $DSN\memory\Debug\

• Press the OK button

|

D.6 How to use Verilog PLI

• Now you can compile the mem_PLI.v

file

there should not be any warning or error messages.

• Compile the mem_tb.v file

• Set the mem_tb module as top level

• Initialize simulation and add signals to

the Waveform

there will be a message reading that the PLI library has been loaded

PLI: Loading library 'C:\My_designs\mem/memory/Debug/memory.dll'

• Run the simulation

• Compare simulation results with the PLI use and plain Verilog description from mem.v (run the simulation again but compile mem.v instead of mem_PLI.v)

Appendix E

WAVES Testbenches

E.1 WAVES Testbenches

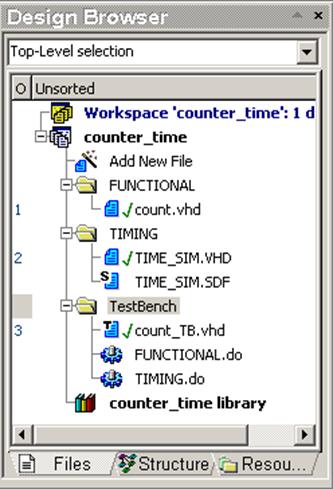

• Open the sample design counter_time

There are three subfolders:

- FUNCTIONAL – contains functional model of a counter

- TIMING – contains timing model of the counter and SDF file

- TestBench – contains testbench and simulation macros

E.2 WAVES Testbenches

• Execute the FUNCTIONAL.do macro

Functional simulation will be run

• Save the waveform as FUNCTIONAL.awf

• Close the waveform file

• Execute the FUNCTIONAL.do macro

Functional simulation will be run

• Save the waveform as FUNCTIONAL.awf

• Close the waveform file

E.3 WAVES Testbenches

• Execute theTIMING.do macro

Timing simulation will be performed

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.