You can also do it by selecting the architecture in the Design Browser and choosing the Generate Testbench option from the pop-up menu.

6.18 Using Testbench Wizard

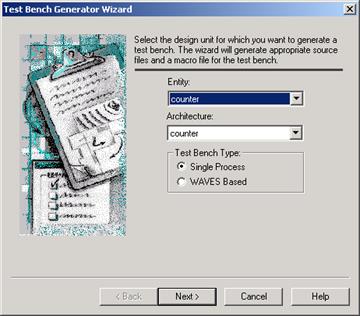

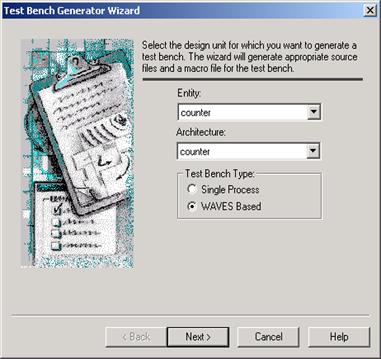

• Select the Counter architecture and the Single Process option in the first wizard window and advance by clicking the Next button.

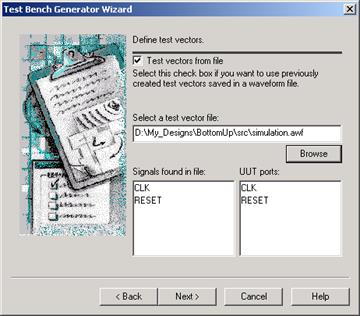

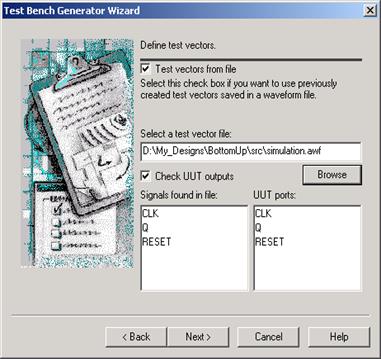

• Check the Test vectors from file option in the next window.

• Open the file with the previously generated waveform.

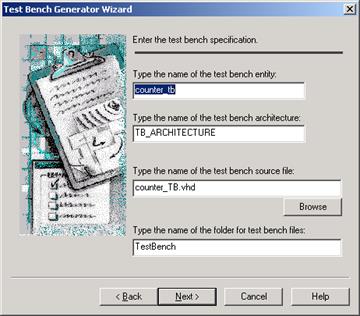

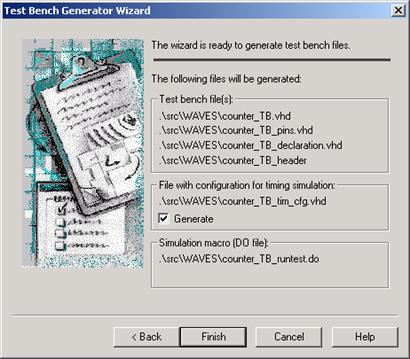

• Click the Next button twice accepting the default options.

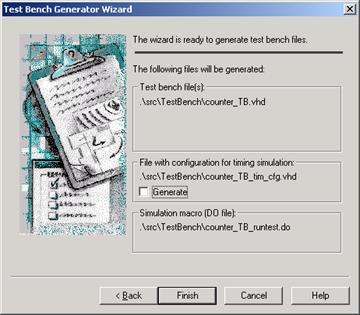

• Finish generation by clicking the Finish button.

6.19 Using Testbench Wizard

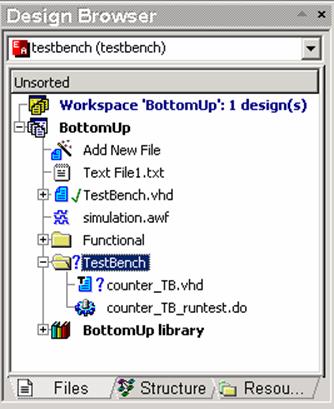

The testbench wizard has created a folder Testbench that is visible on the Files tab of the Design Browser window. It contains two files.

• Counter_TB.vhd – the testbench file

• Counter_TB_runtest.do– the macro command file that compiles the design and

executes the testbench for simulation.

6.20 Using Testbench Wizar

The complete Counter_TB.vhd testbench file content is shown in the figure.

Observe that the clocking and reset processes were replaced by one STIMULUS process that contains a sequence of assignments and wait instructions.

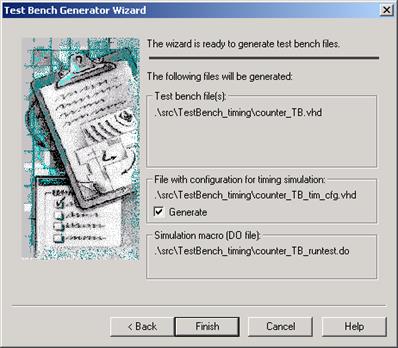

6.21 Testbench for Timing Simulation

You can use the same waveform file to create a testbench for timing simulation. To do that, you must call the testbench wizard as described before. In the last wizard window, check the Generate check box to generate the timing simulation configuration testbench file. This time the Testbench folder will contain three files:

• Counter_TB.vhd – the testbench file

• Counter_TB_tim_cfg.vhd – the

testbench file for timing simulation

• Counter_TB_runtest.do – the macro

command file that compiles the

design and executes the testbench for

simulation.

6.22 Testbench for Timing Simulation

Timing simulation can be performed after the synthesis and Place&Route processes are finished. They can generate a VHDL netlist file for timing simulation.

To enable timing simulation, you must change the contents of the timing configuration testbench to reflect the name of the VHDL netlist. The Counter_TB_tim_cfg.vhd file contains the following configuration:

• You only need to uncomment the use line and change the architecture and entity names, accordingly.

6.23 Testbench for Timing Simulation

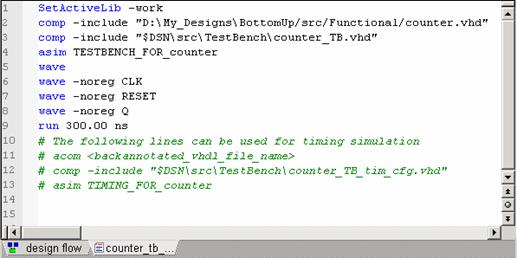

The Counter_TB_runtest.do requires some modifications to run the timing simulation. Uncomment the three last lines in the file and move them up to the top of the file. You should also comment the next three lines as shown in the picture. The macro file will now compile the design and run it for timing simulation.

6.24 WAVES Testbench

• The WAVES-based testbench simultaneously drives the inputs and compares the output response with a previously saved pattern.

• During simulation, the test vectors (stimulus and output response) are taken from the test vector file (*.VEC).

• The Testbench Wizard generates the test vector file (*.VEC) from a waveform file (*.AWF) created using the Waveform Editor.

• Typically, a WAVES testbench is used to create a testbench during the design stage and during design development.

• The second possibility is to use WAVES testbenches to compare timing and functional simulation results.

• The WAVES testbench is compliant with the IEEE Standard and can also be used in the electrical test environment.

6.25 WAVES Testbench

• Select the Counter architecture and WAVES-based option in the first wizard window and advance by clicking the Next button.

• Check the Test vectors from file option in the next window.

• Open the file with the previously generated waveform.

• Click the Next button twice accepting the default options.

• Check the Generate option and click the Finish button.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.