• The method of measurement is to compare input signal frequency with a reference clock signal that is slower than the measured signal.

• To measure the input frequency, you need to set the START signal to 1 and hold it; setting the START signal back to 0 finishes the measurement and resets the meter for the next measurement cycle.

• The design contains 3 blocks described in behavioral VHDL code, one state diagram and one block diagram.

• A top level block diagram ties all of the blocks together.

• The training is based on a simple frequency meter design with a BCD counter and a 7-segment LED display.

• The method of measurement is to compare input signal frequency with a reference clock signal that is slower than the measured signal.

• To measure the input frequency, you need to set the START signal to 1 and hold it; setting the START signal back to 0 finishes the measurement and resets the meter for the next measurement cycle.

• The design contains 3 blocks described in behavioral VHDL code, one state diagram and one block diagram.

• A top level block diagram ties all of the blocks together.

1.2 Creating a Behavioral Design

• The entire design is described by the following block diagram:

1.3 Creating a Behavioral Design

• The following blocks are used in the design:

– HEX2LED - 7 segment display converter

– CNT_BCD - 4 decades BCD counter block

diagram

(contains CNT_4b modules)

– CONTROL - frequency meter control state machine

– Top_frqm - the top level of the design

1.4 Creating a Behavioral Design

• This section will show the following operations:

– How to use New Workspace wizard to create new workspace

– How to use New Design Wizard to create new design

– How to use New Source File Wizard to create source files

– How to create your own VHDL code

– Basic operations in Design Browser

– Basic operations with Language Assistant

– How to use Signal Alias Editor and Signal Aliases

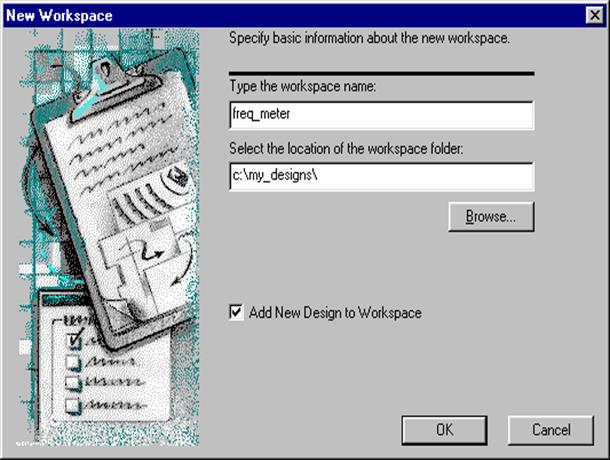

1.5 Creating a Workspace

• Start Active-HDL

• Select the File option from the main menu, then click New | Workspace to invoke the New Workspace wizard window

• In the Type the workspace name field, enter freq_meter

• Leave the Add New Design to Workspace checkbox selected.

• Click the OK button to start the New Design Wizard.

1.6 Creating a Behavioral Design

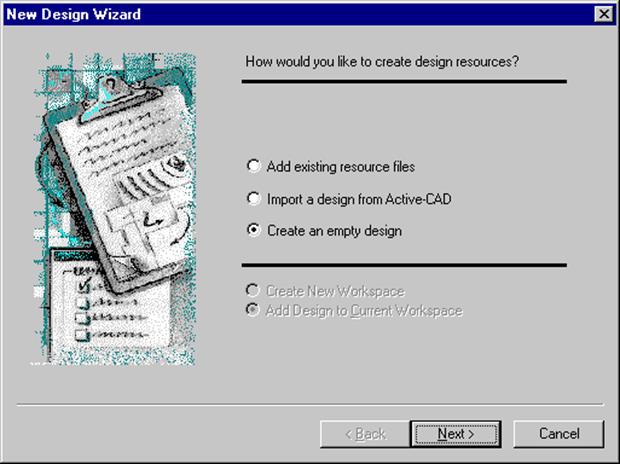

• In the first window of the New Design Wizard, select Create an empty design option

• Click the Next button to advance to the next page

• In the first window of the New Design Wizard, select Create an empty design option

• Click the Next button to advance to the next page

1.7 Creating a Behavioral Design

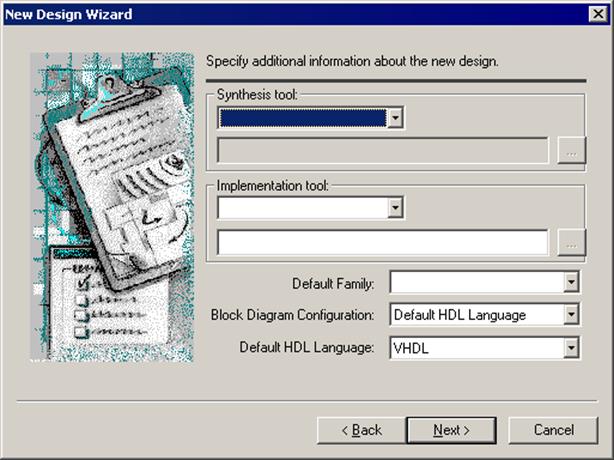

• Because we are not going to use synthesis and implementation tools in this lab, you can leave the Synthesis tool and Implementation tool settings unchanged

• Set the Block Diagram Configuration to ”Default HDL Language” and Default HDL Language to ”VHDL”

• Click the Next button to advance to the next page

1.8 Creating a Behavioral Design

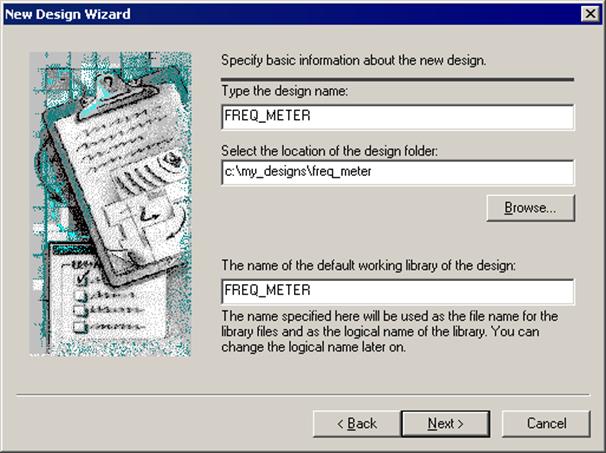

• In the Type the design name field, enter FREQ_METER

• Leave default values in the Select the location of the design folder box and the The name of the default working library of the design box

• Click on the Next button to advance to the next page

• Click Finish in the last window of the Wizard

1.9 Creating a Behavioral Design

• On the File menu click New| VHDL Source to invoke the New Source File Wizard window

• If the Add the generated file to the design box is not checked, select it now

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.