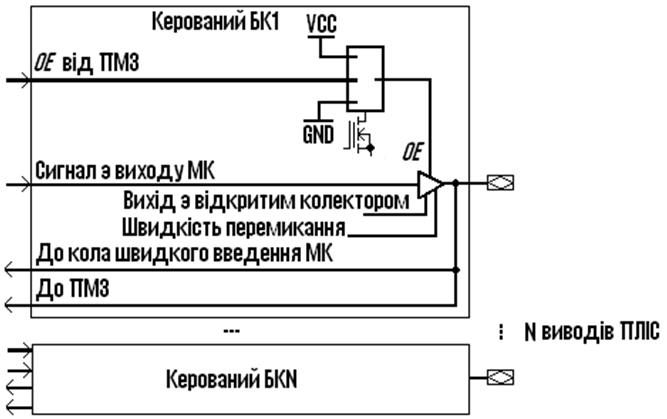

БКВВ складається з однакових керованих буферних каскадів БК1 ... БКN (рис. 9.9), кількість яких визначається числом N контактних площинок, закріплених за даним ЛБ (зазвичай N = 4 ... 16). Напрямок передавання даних програмується мультиплексором.

Рисунок 9.9

Якщо вхід дозволу ОЕ програмуванням з’єднується із землею GND, буфер переводиться до третього стану і від’єднується від контакту, який стає входом: сигнал від нього спрямовується до буферів ПМЗ і є тепер приступним для всіх ЛБ, а також потрапляє до кола швидкого введення макрокомірки (див. рис. 9.8, в). При з’єднанні входу ОЕ з напругою живлення VCC буфер передає (з підвищеною навантажувальною здатністю) сигнал з виходу МК до контакту, який стає тепер виходом ПЛІС. І, нарешті, за допомогою одного із шести глобальних сигналів від ПМЗ здійснюється оперативне керування входом ОЕ в режимі входу/виходу, коли напрямок передавання даних може змінюватися (наприклад, спочатку від контактних площинок приймається адреса, а відтак на них передаються результати обробки інформації).

Крім того, програмуванням буфер можна перетворити в схему з відкритим колектором з метою гнучкості використання його виходу. Є також можливість регулювати швидкість перемикання (Slew Rate) буфера шляхом зміни тривалості фронтів вихідного сигналу. З двох швидкостей перемикання висока забезпечує максимальну швидкодію, але круті фронти перемикання спричиняють при цьому високий рівень завад у вихідній лінії. Тому, коли дозволяють міркування швидкодії, використовують режим положистих фронтів, який завжди запроваджується автоматично під час вмикання джерела живлення.

9.1.2.5 Особливості архітектури ПЛІС із тригерною пам’яттю конфігурації

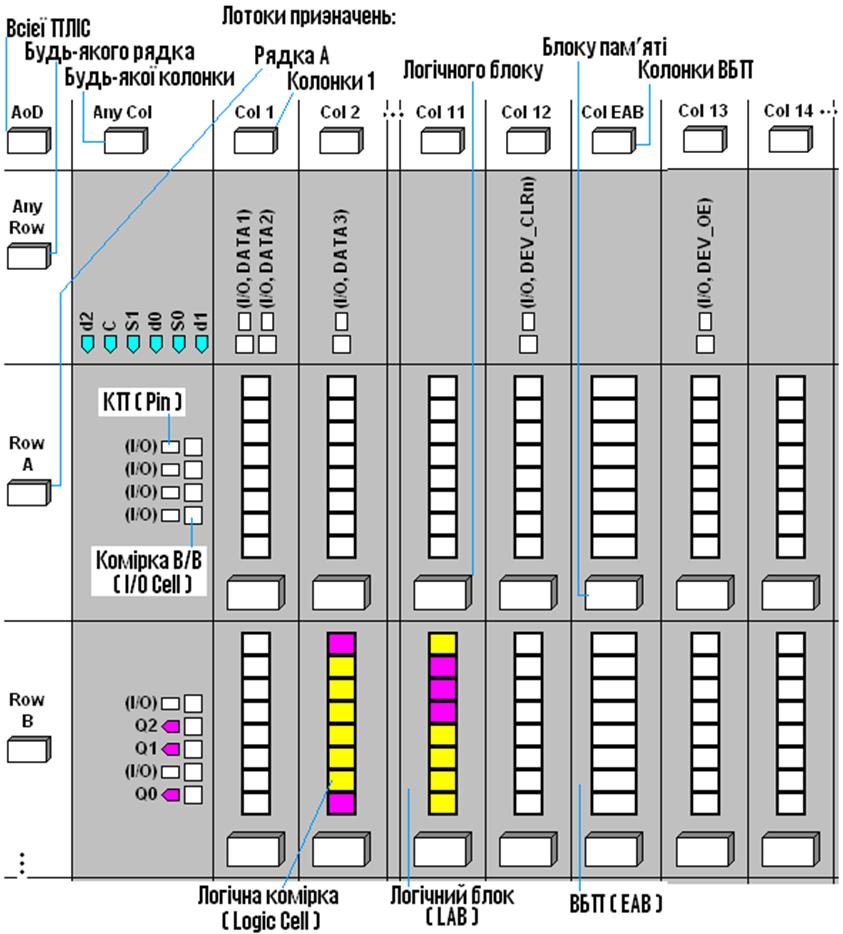

З розвитком технології і зростанням ступеня інтеграції з’явилися ІС комбінованого типу, що поєднують в собі в себе властивості CPLD зі схемотехнікою запам’ятовувальних пристроїв. Прикладом є популярна ПЛІС родини FLEX 10K фірми Altera (FLEX – Flexible Logic Element Matrix – гнучка матриця логічних елементів), план розміщення якої (Floorplan) подано на рис. 9.10. Як і для ПЛІС типу CPLD (див. рис. 6,а), зв’язки між компонентами такої ПЛІС так само можна відображати на її плані графічно або логічними рівняннями.

Призначення (Assignments) для компонентів містяться в лотоках, пояснення яких винесено на плані вгорі. Крім логічних блоків ЛБ (Logic Array Block, LAB) до складу ІС входять також вбудовані блоки пам’яті ВБП (Embedded Array Block, EAB). Логічні блоки розташовано по рядках (Row) і колонках (Col), тому позначаються двокоординатною системою відліку, наприклад, відмічений внизу на плані блок має ім’я „В11”, а блок над ним – ім’я „А11”. ІС містить лише один стовпець блоків пам’яті (розташований всередині між стовпцями ЛБ), тому вони іменуються назвою рядка, наприклад, позначений внизу на плані блок має ім’я „ЕАВ_В”, а блок над ним – ім’я „ЕАВ_А”.

Рисунок 9.10

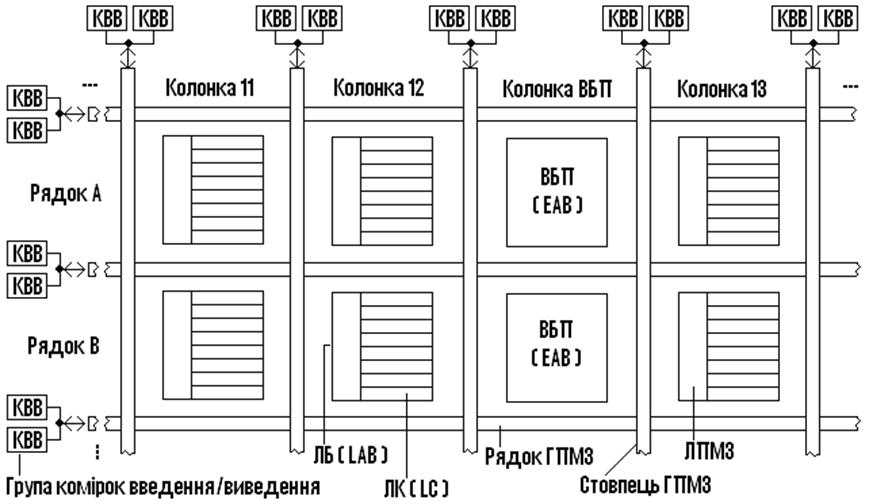

Наступною за ієрархією структурних одиниць є логічна комірка ЛК (Logic Cell, LC), яка в технічній документації для ПЛІС із тригерною пам’яттю конфігурації (SRAM-based) називається логічним елементом ЛЕ (Logic Element, LЕ). Такий „елемент” подібно до макрокомірки має логічну частину і програмований тригер, що є розрядом регістра, але відрізняється тим, що логічна функція реалізується програмуванням її таблиці відповідності в запам’ятовувальному пристрої (табличний спосіб реалізації). Крім того, ЛЕ містить коло переносу (для підвищення швидкодії схем типу лічильників і суматорів) та коло каскадування (для гнучкості формування функцій багатьох змінних кількома комірками). Кожний ЛБ розглядуваного типу ПЛІС містить 8 логічних комірок, які позначаються своїм номером у блоці та його координатами, наприклад, відмічена внизу на плані ЛК має ім’я „LC7_В2”.

Рисунок 9.11

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.