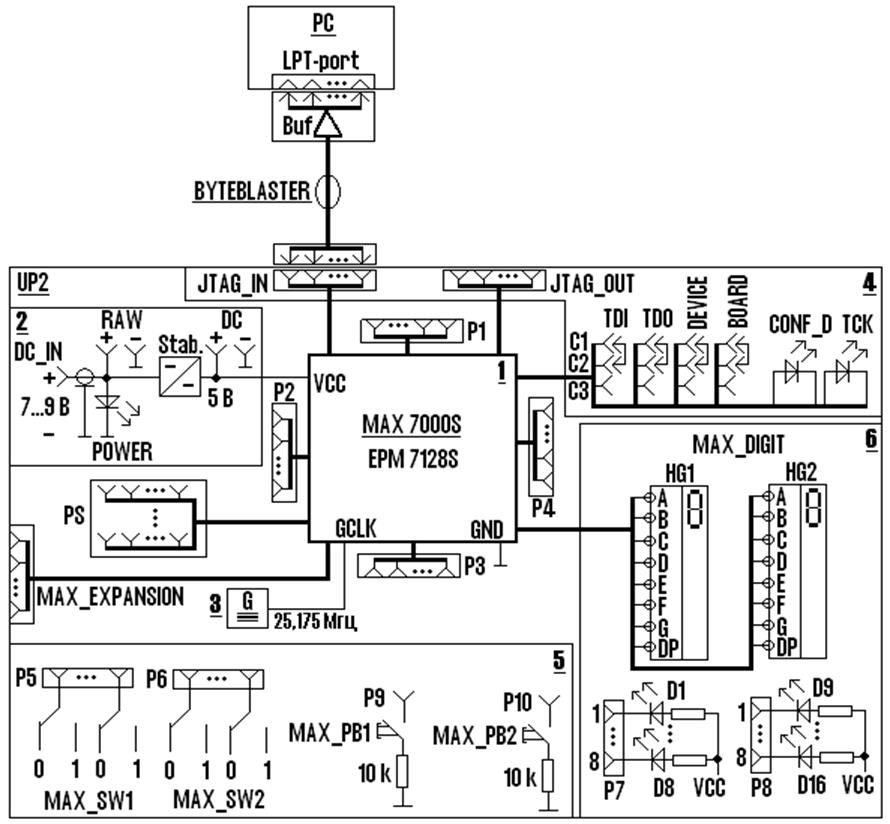

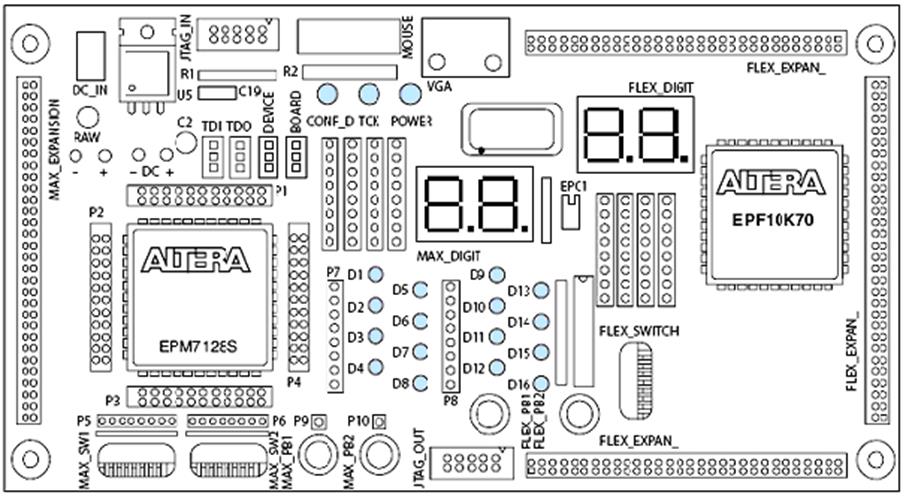

2 Живлення. Через коаксіальний кабель DC_IN до плати подається напруга 7...9 В від зовнішнього нестабілізованого джерела живлення, яке має забезпечувати струм не менше 350 мА. Наявність зовнішньої напруги індикується зеленим світлодіодом POWER, а її величину можна контролювати з контактних площин RAW. Усі компоненти плати живляться напругою VCC = 5 В від вбудованого інтегрального стабілізатора напруги Stab типу LM340T. Стабілізовану напругу можна контролювати з контактних площин DC.

3 Тактовий генератор. На платі є вбудований тактовий генератор G з кварцовою стабілізацією частоти 25,175 МГц. Вихід генератора з’єднано з глобальним синхровходом мікросхеми GCLK (вивід 83).

Рисунок В2

4 Інтерфейс JTAG. Фізичне програмування мікросхеми здійснюється через інтерфейс JTAG, докладно описаний в лабораторній роботі №9. Вхідний рознімач цього інтерфейсу JTAG_IN призначений для з’єднання мікросхеми з комп’ютером через завантажувальний пристрій ByteBlaster II. Як видно з таблиці Б2, до цього рознімача крім програмувальних сигналів підводиться також напруга VCC для живлення буферів Buf, вмонтованих у рознімач пристрою ByteBlaster ІІ. Вихідний рознімач JTAG_OUT інтерфейсу використовується для програмування ланцюжка мікросхем. Режими програмування і конфігурування (таблиця Б3) задаються за допомогою чотирьох штирьових триконтактних перемикачів С1, С2, С3 (на рис. В2 наведено їх положення в режимі програмування однієї мікросхеми), що замикаються перемичками (джамперами). Миготінням світлодіода ТСК індикується передача даних під час програмування, а світінням світлодіода CONF_D – завершення цього процесу.

5 Перемикачі для задання вхідних сигналів. Два задавальні DIP-перемикачі MAX_SW1 і MAX_SW2 (по вісім ключів у кожному), дозволяють сформувати 16 статичних рівнів логічного 0 та 1 на з’єднаних з ними групах контактів Р5 і Р6 (розімкнений стан ключа відповідає рівневі логічної 1, а замкнений – рівневі логічного 0). За допомогою двох нефіксовних кнопкових перемикачів MAX_РВ1 і MAX_РВ2, які під час натискання замикають контакти Р9 та Р10 на землю через резистори 10 кОм, можна сформувати одноразові перепади рівнів, наприклад, на входах скидання або синхронізації. Для подачі сигналів на входи мікросхеми обидва зазначені види перемикачів з’єднують з контактними гніздами дротами.

6 Індикатори вихідних сигналів. Цифровий індикатор MAX_DIGIT на два знакомісця виконано на ІС семисегментних індикаторів зі спільним катодом, отже, сегменти засвічуються рівнем логічного 0. Позначення сегментів пояснюється в 3 розділі, а їх зв’язок з виводами мікросхеми наведено в табл. В4. Крім того, для індикації статичних станів вихідних сигналів плата містить 16 світлодіодів, запалюваних рівнем логічного 0 (струм через них задається резисторами 330 Ом). Світлодіоди D1…D8 з’єднано з контрольними гніздами 1...8 групи Р7; так само з гніздами 1...8 групи Р8 з’єднано діоди D9…D16, відповідно.

Рисунок В3

1ОСНОВНІ ЛОГІЧНІ ФУНКЦІЇ

Мета роботи: дослідження типових логічних елементів; засвоєння основ керування файлами у MAX+plus II; засвоєння основ часового аналізу.

Домашнє завдання

! 1) Засвоїти теоретичні відомості щодо основних логічних функцій, співвідношень алгебри логіки а також арифметичних основ цифрової техніки, необхідних для розуміння логічних схем. Ознайомитися із загальними відомостями щодо пакета MAX+plus II (див. вступ).

2) Визначити, яку логічну функцію виконують схеми з елементом, заданим згідно з варіантом (див. додаткок А, варіанти завдання 1).

1.1 Стислі теоретичні відомості

1.1.1 Основи алгебри логіки

Цифровий пристрій є перетворювачем інформації в тому сенсі, що сигнал на кожному з його виходів залежить від сукупності вхідних сигналів за чітко визначеними правилами. Ці правила описуються мовою алгебри логіки, яка оперує з логічними змінними й функціями (вони називаються також двійковими, бо можуть набувати двох значень: логічного 0 або 1). Отже, алгебра логіки є основою не тільки проектування ЦП, але й розуміння принципу їх дії. Вона використовується також за текстового опису проектів мовами програмування високого рівня HDL (Hardware Description Language – мови опису апаратних засобів), зокрема, мовою AHDL, яка пристосована до ІС фірми Altera. Основні логічні функції та зображення їх мовою AHDL наведено в таблиці 1.1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.