Виводи (контакти, Pin)

мікросхеми, які так само поділяються на спеціалізовані і виводи користувача

(глобальні входи, у разі потреби, можуть використовуватися як звичайні),

розташовано на плані по периметру з усіх боків. При цьому будь-який вивід

користувача (але не глобальні входи) може бути запрограмований як вхід, вихід

або двоспрямований вхід/вихід пристрою за допомогою комірок введення/виведення

КВВ (I/O Cell) біля

кожного з них. Аналогічно блоку керування введенням/виведенням БВВ (див. рис. 9.9)

у КВВ здійснюються функції підвищення навантажувальної здатності, перемикання

напрямку передачі інформації, регулювання режимів буфера (швидкість

перемикання, емуляція схеми з відкритим колектором). Крім того, КВВ містить

вхідний і вихідний регістри для тимчасового зберігання даних та складну систему

перемикання сигналів між шинами (більше десятка програмованих мультиплексорів

та інших елементів).

Виводи (контакти, Pin)

мікросхеми, які так само поділяються на спеціалізовані і виводи користувача

(глобальні входи, у разі потреби, можуть використовуватися як звичайні),

розташовано на плані по периметру з усіх боків. При цьому будь-який вивід

користувача (але не глобальні входи) може бути запрограмований як вхід, вихід

або двоспрямований вхід/вихід пристрою за допомогою комірок введення/виведення

КВВ (I/O Cell) біля

кожного з них. Аналогічно блоку керування введенням/виведенням БВВ (див. рис. 9.9)

у КВВ здійснюються функції підвищення навантажувальної здатності, перемикання

напрямку передачі інформації, регулювання режимів буфера (швидкість

перемикання, емуляція схеми з відкритим колектором). Крім того, КВВ містить

вхідний і вихідний регістри для тимчасового зберігання даних та складну систему

перемикання сигналів між шинами (більше десятка програмованих мультиплексорів

та інших елементів).

Двокоординатна система позначень блоків відповідає дворівневій системі зв’язків між ними за допомогою глобальної програмованої матриці з’єднань ГПМЗ, поділеній на рядки і стовпці (рис. 9.11), з якими з’єднуються комірки вводу-виводу КВВ по всьому периметру ПЛІС. Через рядки і стовпці ГПМЗ, між якими розташовані ЛБ і ВБП, здійснюється обмін даними, а обмін між комірками організовано через локальну програмовану матрицю ЛПМЗ.

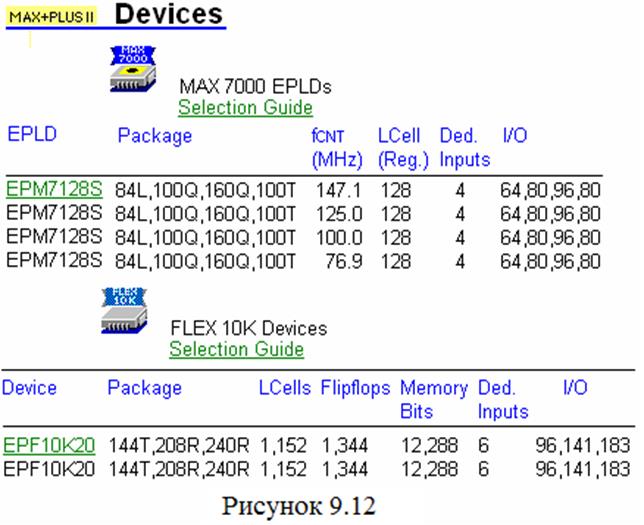

ПЛІС однієї родини, як і EPLD, однотипні і відрізняються лише складністю, що й визначає назву ІС (основні довідкові відомості для двох типів ПЛІС наведено на рис. 9.12). Так, мікросхема EPF10K10 родини FLEX 10K найменшої складності має логічну ємність 10 тис. еквівалентних вентилів (72 ЛБ, 576 ЛК, 3 ВБП обсягом 2048 бітів кожний), а ІС цієї родини EPF10K250 найбільшої (на цей час) складності має логічну ємність 250 тис. еквівалентних вентилів (1520 ЛБ, 12160 ЛК, 20 ВБП). Такі ПЛІС придатні для побудови складних пристроїв обробки інформації.

9.1.3 Програмування і конфігурування

9.1.3.1 Режими програмування і конфігурування

Як вже зазначалося (див. п. 9.1.1.2), структуру ПЛІС можна налаштовувати для реалізації проектів за програмувальними файлами у двох режимах – у режимі програмування (Program) або конфігурування (Configure). Режим програмування застосовується для мікросхем типу EPLD, виготовлених за технологією РПЗП-ЕС (EEPROM), у тому числі такому різновиду як флеш-пам’ять, та РПЗП-УФ (EPROM). Режим конфігурування може застосовуватися для мікросхем, виготовлених за технологією СОЗП (SRAM). Перед перепрограмуванням ПЛІС, що базуються на технології РПЗП-УФ, потрібне попереднє стирання даних ультрафіолетовим промінням з вийманням її з пристрою.

Фізичнепрограмування або конфігурування виконується під дією згенерованих під час компіляції проекту програмувальних файлів, що надходять з комп’ютера. Залежно від установлених опцій програматора MAX+PLUS II в автоматичному режимі реалізуються такі функції: 1) перевірка наявності контакту між мікросхемою і відповідним з’єднувальним пристроєм; 2) перевірка на порожність (Blank-Check), тобто на відсутність перед програмуванням записаної до ІС інформації; 3) програмування (Program) або конфігурування (Configure), яке полягає в завантаженні до ІС даних з програмувального файла і налаштуванні її структури на виконання потрібних функцій; 4) верифікація (Verify), тобто перевірка ІС після програмування на відповідність записаної до неї інформації даним програмувального файла; 5) функціональне тестування запрограмованої ІС (Test) шляхом подачі на її входи комбінацій сигналів згідно із сигнальним файлом та порівняння вихідних сигналів на відповідність їх часовим діаграмам SCF-файла; 6) випробування (Examine), яке полягає в зчитуванні даних від запрограмованої ІС (якщо вона не захищена спеціальним бітом захисту) з можливістю запису їх у власному файлі і подальшого використання, наприклад, з метою з’ясувати причини незадовільної роботи даної ІС або для програмування інших ІС.

9.1.3.2 Інтерфейс JTAG

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.