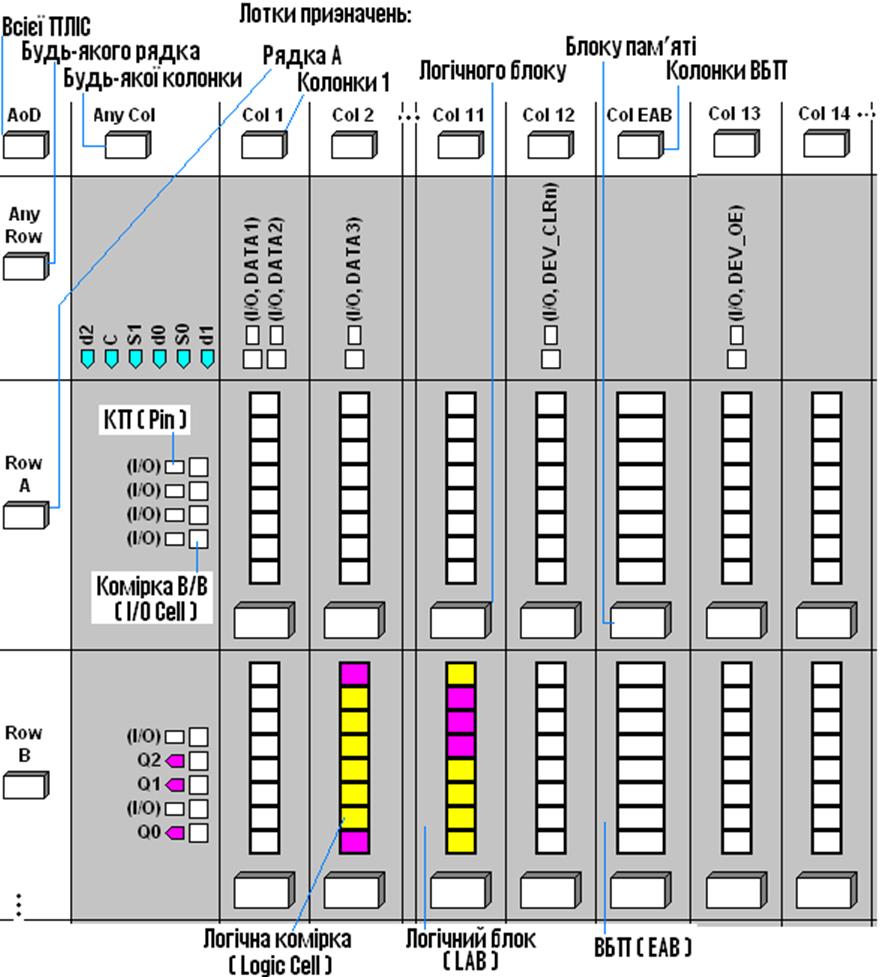

Рисунок 10.3 – План розміщення (Floorplan) ПЛІС FLEX 10K фірми Altera

Виводи (контакти, Pin) мікросхеми, які так само поділяються на спеціалізовані і виводи користувача (глобальні входи, у разі потреби, можуть використовуватися як звичайні), розташовано на плані по периметру з усіх боків. При цьому будь-який вивід користувача (але не глобальні входи) може бути запрограмований як вхід, вихід або двоспрямований вхід/вихід пристрою за допомогою комірок вводу-виводу КВВ (I/O Cell) біля кожного з них. Аналогічно блоку керування вводом-виводом БВВ у КВВ здійснюються функції підвищення навантажувальної здатності, перемикання напрямку передавання інформації, регулювання режимів буфера (швидкість перемикання, емуляція схеми з відкритим колектором). Крім того, КВВ містить вхідний і вихідний регістри для тимчасового зберігання даних та складну систему перемикання сигналів між шинами (більше десятка програмовних мультиплексорів та інших елементів).

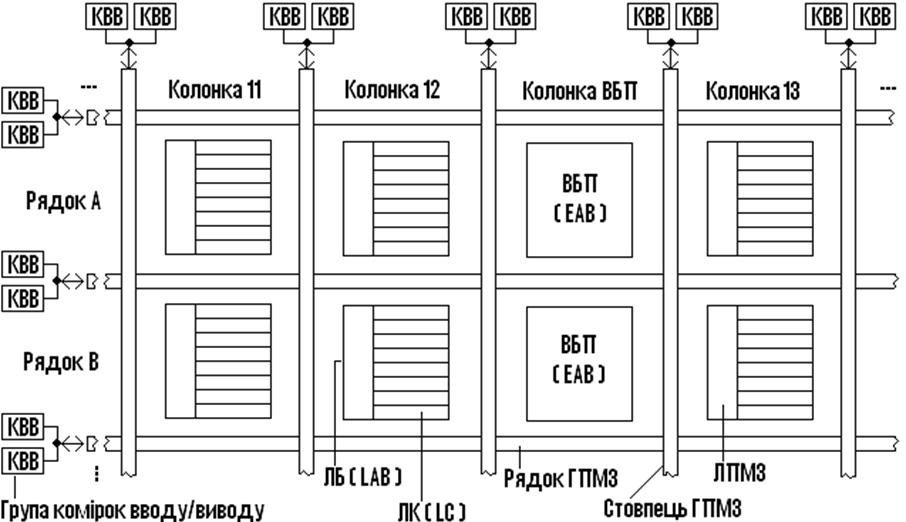

Рисунок 10.4 – Дворівнева система зв’язків блоків за допомогою глобальної програмовної матриці з’єднань ГПМЗ, поділеній на рядки і стовпці

Двокоординатна система позначень блоків відповідає дворівневій системі зв’язків між ними за допомогою глобальної програмовної матриці з’єднань ГПМЗ, поділеній на рядки і стовпці (рис. 4), з якими з’єднуються комірки вводу-виводу КВВ по всьому периметру ПЛІС. Через рядки і стовпці ГПМЗ, між якими розташовані ЛБ і ВБП, здійснюється обмін даними, а обмін між комірками організовано через локальну програмовну матрицю ЛПМЗ.

Довідкові відомості

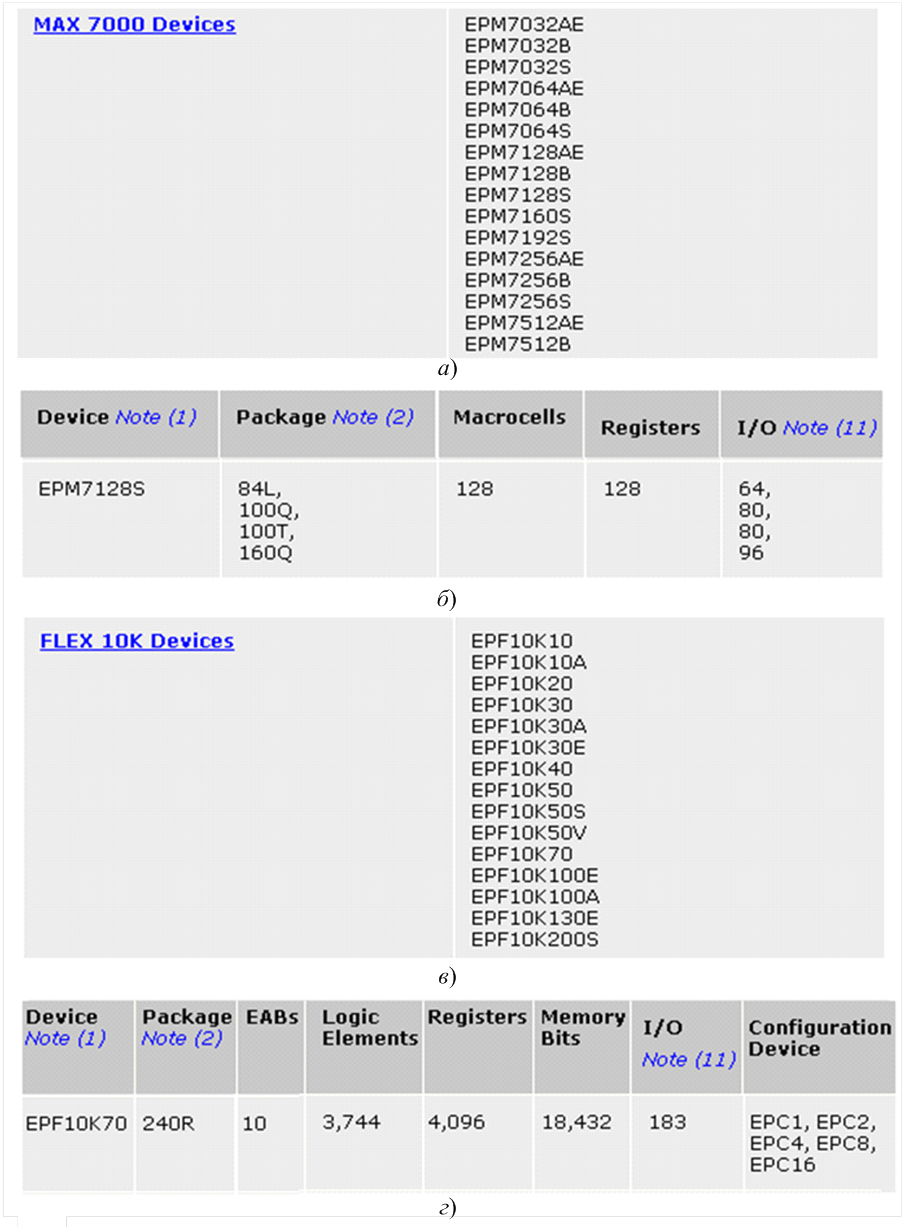

Сім’ї мікросхем подані в довідці пакета Help > Devices & Adapters. ПЛІС однієї родини однотипні і відрізняються кількістю ЛБ. Так, сім’ї МАХ7000 (рис. 10.5,а) найменшої складності містять два ЛБ, а найбільшої складності – 32 ЛБ.

Рисунок 10.5 ─ Довідкові відомості сімей мікросхем

Кожний ЛБ розглядуваного типу ПЛІС складається з 16 макрокомірок, а їх загальна кількість у мікросхемі визначає її назву. Найпростіші мікросхеми типу ЕРМ7032(АЕ, В, S) містять у двох логічних блоках 32 макрокомірки, а найскладніші ЕРМ7512(АЕ, В) – 512 МК у складі 32-х ЛБ.

Натисканням у списку ІС на сім’ю потрібного типу легко вийти на файл довідки з даними про типи корпусів (Package), кількість макроко-мірок (Macrocells) і доступних для користувача виводів (I/O) та інші дані (на рис. 10.5,б подано фрагмент даних для ІС типу EPM7128S сім’ї MAX7000S). Докладну інформацію про цоколівку виводів тощо можна отримати в п. 3 лабораторного завдання або на Altera website (у попередніх версіях Quartus II така інформація міститься в довідці).

У назвах ПЛІС сімей типу FLEX (рис. 10.5,в) складність позначається в тисячах еквівалентних вентилів. Так у сім’ї FLEX 10K мікросхема EPF10K10 найменшої складності має логічну ємність 10 тис. еквівалентних вентилів (72 ЛБ, 576 ЛК, 3 ВБП обсягом 2048 біт кожний), а ІС цієї сім’ї EPF10K250 найбільшої складності має логічну ємність 250 тис. еквівалентних вентилів (1520 ЛБ, 12160 ЛК, 20 ВБП).

Такі ПЛІС придатні для побудови складних пристроїв оброблення інформації. У довідці для ІС такого типу (на рис. 10.5,в подано фрагмент даних для ІС типу EPF10K70 сім’ї FLEX 10K) макрокомірки називаються «логічними елементами» (Logic Elements) та подаються також відомості щодо вбудованих блоків пам’яті (EABs) і типи конфігураційних мікросхем (Configuration Device), призначених для зберігання інформації про конфігурацію ІС, яка після ввімкнення джерела живлення автоматично завантажується до ПЛІС.

КОНТРОЛЬНІ ЗАПИТАННЯ

1. Спроектуйте подільник частоти на 60 на основі: а) макрофункцій двійкових лічильників; б) макрофункцій декадних лічильників; в) макрофункцій подільників частоти; г) макрофункцій JK-тригерів (безвентильний); д) макрофункцій цифрових таймерів; е) мегафункції лічильника.

2. Чим відрізняються сучасні програмовні ПЛІС від мікропроцесорних ІС, робота яких основана на виконанні програми? Порівняйте можливості таких ІС щодо складності виконуваних функцій і швидкодії.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.