Рисунок 8.7 – Фрагменти випробування РІР щодо самовідновності

КОНТРОЛЬНІ ЗАПИТАННЯ

1. Тригери якого типу керування можна застосовувати в паралельних регістрах і регістрах зсуву?

2. Побудуйте на тригерах: а) JK-; б) RS-; в) D-типу такий трирозрядний регістр: 1) паралельний; 2) зсуву (послідовно-послідовний); 3) паралельно-послідовний; 4) послідовно-паралельний; 5) реверсивний; 6) кільцевий; 7) універсальний; 8) буферний з трьома станами виходу.

3. Користуючись умовними графічними позначеннями, складіть з ІС 4-розрядних регістрів схему 12-розрядного регістра: а) паралельного; б) зсуву.

4. Перетворіть трирозрядний паралельний регістр у регістр зсуву.

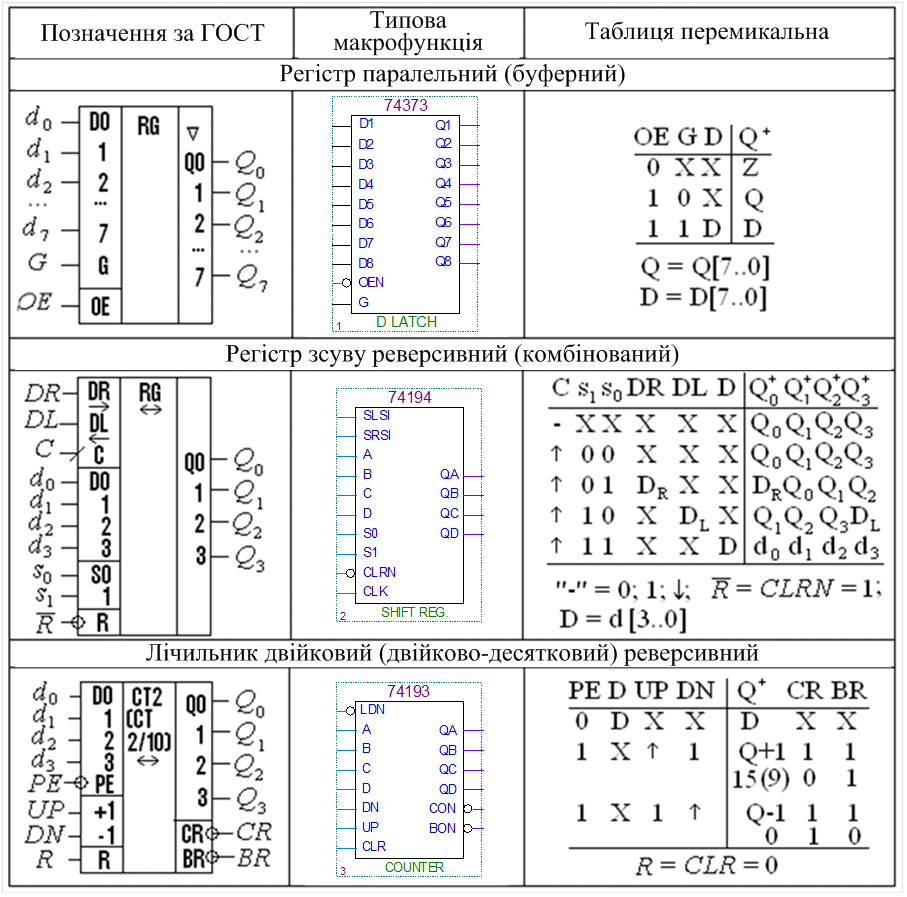

Таблиця 8.1 – Макрофункції послідовнісних пристроїв

Таблиця 8.2 – Мегафункції послідовнісних пристроїв

|

Символ |

Основні параметри |

|

|

lpm_latch/lpm_ff – паралельні регістри зі статичним/динамічним керуванням; lpm_shiftreg – регістр зсуву (універсальний реверсивний регістр): LPM_WIDTH – розрядність вхідної data[] і вихідної q[] шин; LPM_AVALUE/LPM_SVALUE – константа для асинхронного/синхронного завантаження; LPM_FFTYPE – тип тригерів: DFF або TFF; LPM_DIRECTION – напрямок зсуву: ліворуч/праворуч ("LEFT"/"RIGHT"); асlr/sclr, aset/sset – входи асинхронного/синхронного скидання до q+[] = 0...0 та передустановлення до q+[] = 1...1 або до q+[] = LPM_(A/S)VALUE; load – вхід синхронного паралельного завантаження q+[] = data[]; enable – дозвіл на проходження синхроімпульсів clock; shiftin, shiftout – вхід/вихід послідовного введення/виведення. |

|

|

lpm_counter: LPM_WIDTH, LPM_AVALUE/LPM_S-VALUE, асlr/sclr, aset/sset – те саме, що і в регістрів; LPM_MODULUS – модуль лічби; LPM_DIRECTION, updown – напрямок лічби: додавання (up) або віднімання (down); aload/sload – входи асинхронного/син-хронного паралельного завантаження q+[] = data[]; clk_en та cnt_en – дозвіл на проходження лічильних імпульсів clock та дозвіл лічби. |

ЛАБОРАТОРНЕ ЗАВДАННЯ

1. Дослідити основні типи регістрів.

1.1 Дослідити паралельний регістр з трьома станами виходів на основі D-тригерів зі статичним керуванням: за принциповою електричною схемою та осцилограмами сигналів (файли 8par.bdf, .vwf) визначити умови режимів запису, зберігання та зчитування інформації, виміряти затримку перемикання. У звіті навести також умовне графічне позначення за ГОСТ такого регістра зі стислим поясненням принципу його дії та осцилограми сигналів.

1.2 Дослідити регістр прямого зсуву (зсуву направо) на D-тригерах з динамічним керуванням (схема 1) у режимах послідовного запису, паралельного та послідовного зчитування (файли 8zsuw.bdf, .vwf) та розглянути особливості побудови і перемикання регістра зсуву наліво (зворотного зсуву) і реверсивного регістра (схеми 2, 3).

1.3 Ознайомитися з різновидами регістрів бібліотеки бази даних (файл 8lіbr.bdf): макрофункціями (вибраними ІС серії 74) паралельних регістрів і регістрів зсуву та мегафункціями. У звіті навести функціональні прототипи (FUNCTION), таблиці відповідності та інші довідкові дані регістрів з кожної групи, пояснити призначення та особливості входів і виходів.

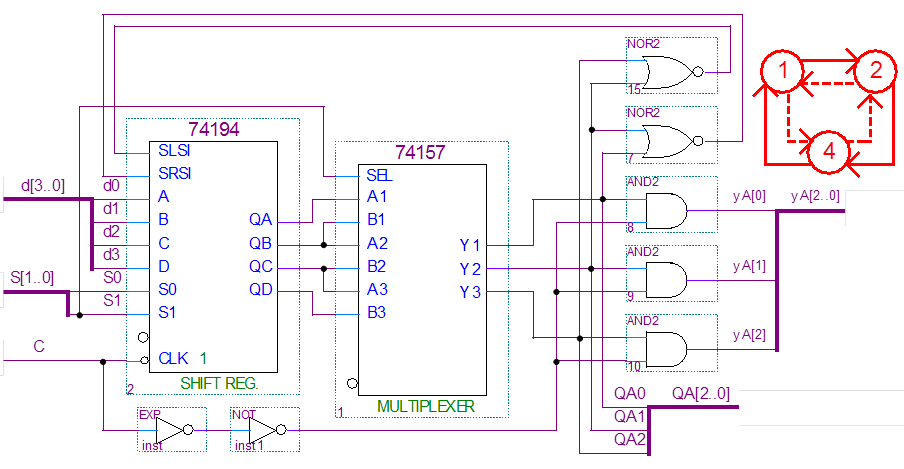

2. Застосувати регістр зсуву в графічному редакторі для побудови заданого варіанта ХХ генератора кодової послідовності (ГКП) або розподільника імпульсів/рівнів (РІР).

2.1 Зібрати найпростіший (несамовідновний) пристрій на макрофункції регістра зсуву вибраного типу в графічному файлі 8XXgkp(ri)1.bdfпроекту8XХgkp(ri)1, виконати компіляцію і моделювання та випробувати його на самовідновність за часовими діаграмами 8XXgkp(ri)1.vwf.

Приклади: 800gkp1.bdf, vwf (схема 1); 800ri1.bdf, vwf (схема 1).

F Примітки:

1. У наведених прикладах пристрій переводиться до станів поза робочим циклом шляхом паралельного завантаження коду зі входів di сигналом MODE=1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.