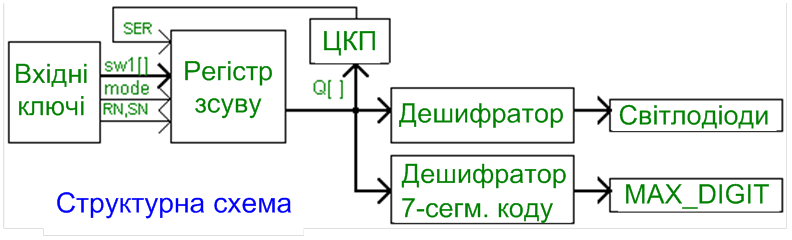

5. Створити проект лабораторного макета на рівні блок-схеми для експериментального дослідження ГКП (РІР) на основі регістра зсуву згідно зваріантом завдання 8(див. структурну схему і як взірець файл 800GENERATOR_KP.bdf – рис. А.6 у додатках).

Схема власне ГКП складається з регістра зсуву і ЦКП. Виходи пристрою через дешифратор семисегментного коду з’єднано із цифровим індикатором для індикації кодів у десятковій системі і через дешифратор – для відображення розрядів на світлодіодах (у прикладі утворено дві гірлянди по колу). Синхросигнал утворюється антидеренчливим пристроєм одноразовим натисненням по черзі ключів на входах RN, SN. Для переведення ГКП до стану поза основним циклом з метою перевірки його на самовідновність від вхідних ключів у паралельному коді записується слово sw1[] (натисненням ключа на вході mode, одноразовим натисненням по черзі ключів на входах RN, SN і відтисненням ключа на вході mode).

5.1 В окремому проекті 8XXGENERATOR_KP(RIR) відтворити ГКП (РІР) за п. 2.2 (шляхом копіювання частини файлів) на мікросхемі сім’ї MAX7000S, типу EPM7128SL84-7. Включити до складу проекту файл дешифратора 7-сегментного коду ../7lab/dc7seg.bdf та створений в окремому файлі і згорнутий до символа дешифратор. Імпортувати призначення виводів мікросхеми з файлу ../4lab/MAX_pin та скоригувати їх. Виконати компіляцію і функціональне моделювання з метою переконатися в правильності проектування.

Приклад: 800GENERATOR_KP.bdf, vwf; 800dc.bdf, .bsf.

5.2 Створити програмувальний CDF-файл, перевірити режим і схему програмування, переконатися, що чотири джампери на платі TDI, TDO, DEVICE, BOARD встановлено в режим програмування однієї мікросхеми та виконати її програмування.

Приклад: 800GENERATOR_KP.сdf.

5.3 Розробити методику та виконати експериментальні дослідження пристрою назапрограмованій ІС. Порівняти результати експериментальних досліджень з даними проектних файлів, зробити висновки.

9 ЛІЧИЛЬНИKИ

Мета роботи: дослідження типових лічильників; застосування лічильників у проектах; засвоєння методів створення недвійкових лічильників і подільників частоти.

ДОМАШНЄ ЗАВДАННЯ

! Спроектувати згідно з варіантом завдання 9 (див. додатки):а) недвійковий лічильник шляхом перетворення двійкового лічильника; б) недвійковий лічильник на тригерах зі зворотними зв’язками.

СТИСЛІ ТЕОРЕТИЧНІ ВІДОМОСТІ

Означення, класифікацію і параметри лічильників, схемну реалізаціюдвійкових лічильників з послідовним, паралельним і груповим переносом, а також принцип побудови реверсивних лічильників викладено в [2]. Тут розглянемо проектування недвійкових лічильників.

Перетворення двійкових лічильників у недвійкові

Якщо в n-розрядному двійковому лічильнику з модулем 2n виключити Мн = 2n – М надлишкових станів, то він перетвориться в недвійковий з модулем М < 2n. Тому потрібна кількість розрядів n двійкового лічильника для утворення недвійкового з модулем М обчислюється в САПР як

n = Ceil(log2M), (9.1)

де Ceil(ceiling – стеля) – найближче ціле число, що не менше виразу в дужках, наприклад, Ceil(log25) = 3. Або простіше вручну розрядність можна визначити з умови

2n-1 < М < 2n, (9.2)

наприклад, недвійковий лічильник з модулем М = 5, виходячи з 22 <5 < 23, можна утворити з трирозрядного двійкового лічильника, якщо усунути Мн = 2n – М = 23 – 5 = 3 надлишкові стани.

Існує кілька методів перетворення двійкових лічильників у недвійкові залежно від способу усунення надлишкових станів. Лічильник з природним порядком лічби утворюється виключенням старших надлишкових станів N = =M, … , 2n – 1 шляхом примусового скидання двійкового лічильника. Принцип такого перетворення розглянемо спочатку на ІС жорсткої структури, коли доступними є лише її зовнішні виводи, зокрема, вхід скидання двійкового лічильника R(рис. 9.1,а). З надходженням лічильних імпульсів С вихідний код зростає в межах N = 0, 1, ..., М і перетворюється в дешифраторі в унітарний код. Коли на виході, номер якого збігається з модулем лічби М, з’являється активний рівень RM, лічильник скидається до нуля і далі цикл лічби повторюється. Стан N = М, в якому лічильник перебуває короткочасно, не використовується, тому кількість фіксованих станів N = 0, 1, ..., М – 1 становить потрібний модуль лічби М.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.