У [2] викладено загальні відомості про сучасні ПЛІС (їх класифікацію за способами програмування структури, програмовні елементи ПЛІС, принцип побудови програмовних логічних матриць), елементи структури (макрокомірка, блок керування вводом/виводом), а також відомості щодо програмування і конфігурування (режими програмування і конфігурування, інтерфейс JTAG, схеми програмування і конфігурування). Тут розглянемо стисло питанняархітектури ПЛІС і наведемо для прикладу відомості про дві сім’ї ПЛІС фірми Altera з довідки САПР Quartus II.

Архітектура ПЛІС

1.1 План розміщення ПЛІС.

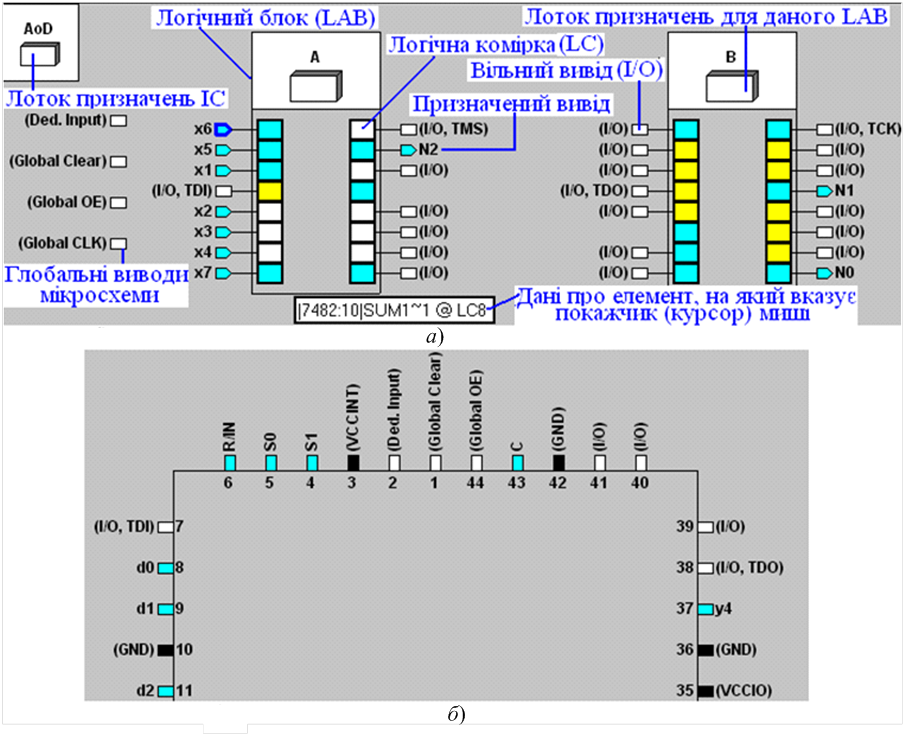

ПЛІС, що крім багатьох програмовних логічних матриць (ПЛМ) містить регістри, буфери, розгалужену систему програмовних з’єднань тощо, структурована на окремі частини. У загальному вигляді ці частини зображаються в САПР на плані її розміщення (Floorplan) як подано на рис. 1,а. Компілятор автоматично призначає елементи схеми, необхідні для реалізації проекту, виконує потрібні з’єднання і вносить всю цю інформацію до об’єктного файлу (після цього проектувальник має змогу скоригувати призначення вручну і знов перекомпілювати проект). Призначення (Assignments) для мікросхеми на плані розміщення містяться в лотку AoD (Anywhere on Device) і відображаються при натисканні на нього.

Найбільшою функціональною частиною ПЛІС є логічний блок ЛБ (Logic Array Block, LAB), в якому згруповано набір логічних ресурсів таким чином, що будь-який сигнал є доступний для кожного елемента набору. На плані ЛБ позначено літерами А, В біля лотків, в яких відображаються призначення відповідного блоку. ІС можуть вміщувати до 32 ЛБ.

Наступною за ієрархією складовою частиною є логічна комірка ЛК (Logic Cell, LCELL, LC), яка в технічній документації для ПЛІС з електричним стиранням (EЕPROM-based) називається макрокоміркою МК (Macrocell, MC). Призначені (задіяні) комірки на плані зафарбовується, а вільні залишаються білими.

Рисунок 10.1

Так само і виводи (контакти, штирки – Pin) мікросхеми на плані (див. рис. 10.1,а) і на цоколівці (на рис. 10.1,б подано її фрагмент), що є призначені, зафарбовані, а вільні – білі. Основна їх частина належить до входів/виходів користувача (User I/O Pins), позначається на вільних виводах у дужках як (І/О), а на призначених виводах – їх іменами відповідно до проектного файлу. Інші виводи є спеціалізовані (Dedicated). Перш за все це GND – земля та VCC або VCCINT і VCCIO – напруги живлення; ці виводи, як і незадіяні (N.C. – No Connect), якщо вони є, наводяться лише на цоколівці (виводи GND у схемі не можна залишати вільними, навіть якщо їх декілька). Наступна група спеціалізованих виводів, призначена для фізичного програмування (TDI, TDO, TCK, TMS), є недоступною для користувача. І, нарешті, остання група спеціалізованих виводів для так званих глобальних сигналів, до яких належать спільні для всіх ЛБ сигнали, зображається на плані окремо від них (у нас – зліва). Типовими є такі глобальні сигнали: GCLK – Global Clock (спільний синхровхід), GCLRn – Global Clear (спільний сигнал скидання, зазвичай інверсний), Global OE – дозвіл виходу для компонентів з трьома станами, Ded. Input (від Dedicated – спеціалізований) – глобальний вхід за призначенням користувача.

Будь-який вивід ІС, розташований на плані біля комірки, може бути запрограмований як вхід або вихід пристрою (у разі потреби, як двоспрямований вхід/вихід). Якщо певний контакт стає виходом (на плані позначається стрілкою, що виходить з ЛБ), він закріплюється за суміжною з ним коміркою, яка стає кінцевою і остаточно формує для нього сигнал (такі комірки зафарбовані блакитним кольором). Якщо ж контакт стає входом (позначається стрілкою, що входить до ЛБ), він не закріплюється за певною МК, а зв’язується з будь-якими комірками через програмовні матриці з’єднань. Так само МК, призначені як проміжні (зафарбовані жовтим кольором), що беруть участь у формуванні проміжної логіки, обмінюються вхідними і вихідними даними з виводами і з іншими комірками через програмовні матриці з’єднань. Деякі МК, що не мають суміжних виводів (у нашій ПЛІС дві таких МК) не можуть бути запрограмовані як кінцеві.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.