1.2 Структура ПЛІС з електричним стиранням (EPLD).

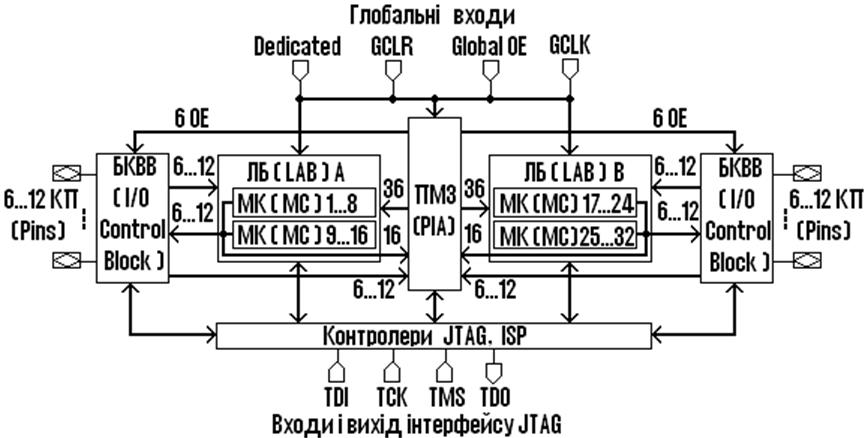

Зв’язки між компонентами ПЛІС відображаються на її плані графічно (кольоровими лініями) або логічними рівняннями (у спеціальному вікні на частині екрана). Проте наочніше такі зв’язки можна показати на структурній схемі як дещо спрощено подано на рис. 10.2 для типової ПЛІСіз електричним стиранням (типу EЕPROM-based EPLD) найменшої складності (ширина шин і кількість елементів, позначених цифрами, у ПЛІС різного типу можуть відрізнятися). Структура складнішої ПЛІС така сама: програмовна матриця з’єднань ПМЗ є спільною і продовжується вниз, а збоку ярусами розташовуються логічні блоки ЛБ, кожний зі своїм блоком керування вводом/виводом БКВВ. Показані знизу інтерфейсні кола і сигнали діють у режимі програмування.

Рисунок 10.2 – Зв’язки між компонентами ПЛІС

Основні зв’язки між структурними складниками ПЛІС здійснюються через ПМЗ, до якої в робочому режимі надходять глобальні сигнали зі спеціалізованих входів безпосередньо (показано вгорі; у деяких ПЛІС може бути два синхровходи для організації двотактних схем), інформаційні сигнали з контактних площинок КП входів/виходів загального користування через БКВВ (показано збоку нижніми шинами розрядністю 6...12 – за кількістю КП, що обслуговуються даним ЛБ) та сигнали з виходів макрокомірок ЛБ (показано 16-розрядними шинами – за кількістю МК у кожному ЛБ).

Усі сигнали ПМЗ стають доступними для макрокомірок кожного ЛБ: потрібні з них програмуванням ПМЗ вводяться до блоків 36-розрядними шинами. Крім того, з метою підвищення швидкодії ЛБ можуть одержувати сигнали колами швидкого введення безпосередньо з глобальних входів і з контактних площинок через БКВВ (шини розрядністю 6...12). У логічних блоках відбувається оброблення інформації і її остаточні результати виводяться на КП через БКВВ (шини 6...12), а проміжні результати надходять до ПМЗ (шини 16) для передавання до інших блоків, в яких завершується оброблення.

Блоки керування вводом/виводом БКВВ програмуються на введення інформації (КП стають входами) або на її виведення (КП стають виходами). Під дією шести глобальних сигналів дозволу виходу, що надходять з ПМЗ (шина 6 ОЕ), досягається гнучкість керування блоком.

1.3 Особливості архітектури ПЛІС із тригерною пам’яттю конфігурації.

З розвитком технології і зростанням ступеня інтеграції з’явилися ІС комбінованого типу, що поєднують в собі властивості CPLD зі схемотехнікою запам’ятовувальних пристроїв. Прикладом є популярна ПЛІС сім’ї FLEX 10K фірми Altera (FLEX – Flexible Logic Element MatriX – гнучка матриця логічних елементів), план розміщення якої (Floorplan) подано на рис. 10.3. Як і для ПЛІС типу CPLD (див. рис. 10.1,а), зв’язки між компонентами такої ПЛІС так само можна відображати на її плані графічно або логічними рівняннями.

Призначення (Assignments) для компонентів містяться в лотках, пояснення яких винесено на плані вгорі. Крім логічних блоків ЛБ (Logic Array Block, LAB) до складу ІС входять також вбудовані блоки пам’яті ВБП (Embedded Array Block, EAB). Логічні блоки розташовані по рядках (Row) і колонках (Col), тому позначаються двокоординатною системою відліку, наприклад, відмічений внизу на плані блок має ім’я „В11”, а блок над ним – ім’я „А11”. ІС містить лише один стовпець блоків пам’яті (розташований всередині між стовпцями ЛБ), тому вони іменуються назвою рядка, наприклад, позначений внизу на плані блок має ім’я „ЕАВ_В”, а блок над ним – ім’я „ЕАВ_А”.

Наступною за ієрархією структурних одиниць є логічна комірка ЛК (Logic Cell, LC), яка в технічній документації для ПЛІС із тригерною пам’яттю конфігурації (SRAM-based) називається логічним елементом ЛЕ (Logic Element, LЕ). Такий елемент подібно до макрокомірки має логічну частину і програмовний тригер, що є розрядом регістра, але відрізняється тим, що логічна функція реалізується програмуванням її таблиці відповідності в запам’ятовувальному пристрої (табличний спосіб реалізації). Крім того, ЛЕ містить коло переносу (для підвищення швидкодії схем типу лічильників і суматорів) та коло каскадування (для гнучкості формування функцій багатьох змінних кількома комірками). Кожний ЛБ розглядуваного типу ПЛІС містить 8 логічних комірок, які позначаються своїм номером у блоці та його координатами, наприклад, відмічена внизу на плані ЛК має ім’я „LC7_В2”.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.