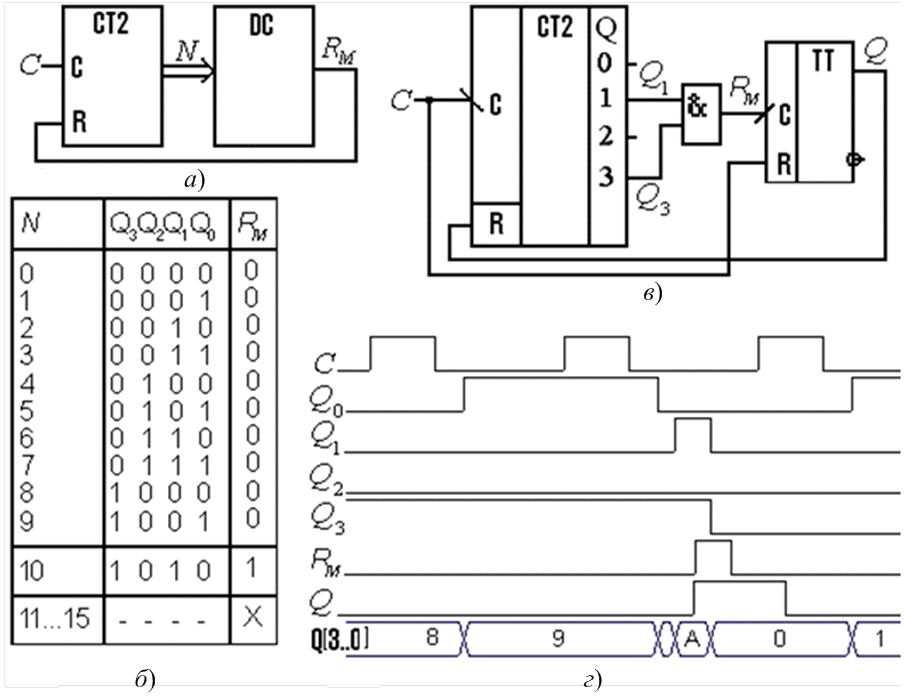

Методику проектування розглянемо на прикладі перетворення двійкового лічильника в декадний з модулем М = 10.

Рисунок 9.1 – Перетворення двійкових лічильників у недвійкові

1. За співвідношеннями (9.1, 9.2) визначаємо потрібну кількість розрядів n = 4 і вибираємо ІС лічильника зі входом скидання.

2. Для наочності зазначаємо в перемикальній таблиці (рис. 9.1,б), що коли лічильник переходить до стану N = М = 10, виникає сигнал скидання RM = 1, яким він повертається до нульового стану, тому старші коди N = 11 ... 15 не використовуються.

3. Мінімізуємо звичайним чином за діаграмою термів шукану функцію RM = Q1Q3, згідно з якою дешифрування виконує елемент І (рис. 9.1,в).

Проте якщо сигнал RM подати безпосередньо на вхід скидання лічильника R, певні його розряди можуть скинутися раніше інших, внаслідок чого на виході елемента І встановиться пасивний рівень, коли лічильник не встигне повністю заповниться нулями. У випадку можливості такої небезпеки слід розширити сигнал RM затримкою на виході елемента І, наприклад, за допомогою додаткового тригера (див. рис. 9.1,в). Вихідним кодом N = Q[3..0]=1010 = А16 встановлюється сигнал RM = 1 (рис. 9.1,г), позитивним перепадом якого тригер перемикається до стану Q = 1 і запам’ятовує його до надходження нового імпульсу С. За цей час лічильник надійно заповнюється нулями, а за позитивним перепадом наступного імпульсу С тригер скидається до стану Q = 0, відновлюється пасивний рівень на вході R лічильника, тому за негативним перепадом імпульсу С починається новий цикл лічби.

Програмовні недвійкові лічильники

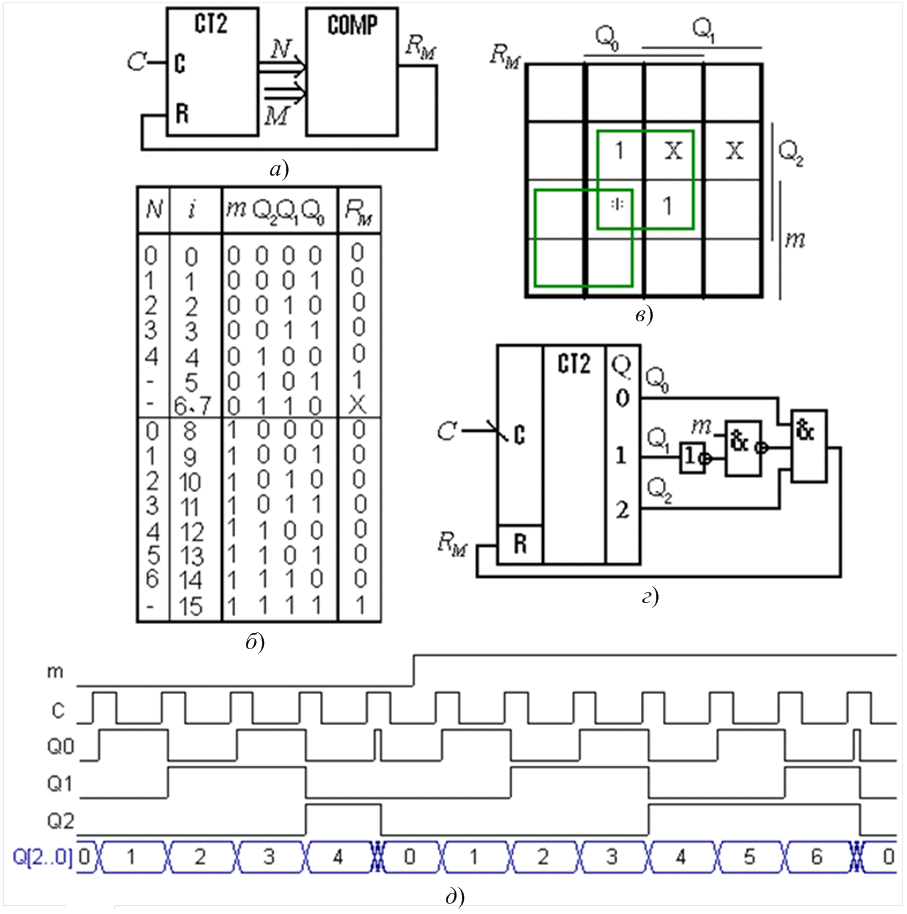

Програмовний лічильник за методом примусового скидання двійкового лічильника можна побудувати заміною дешифратора в узагальненій схемі перетворення (див. рис. 9.1,а) на цифровий компаратор (рис. 9.2,а). Коли, під час лічби вихідний код N сягає потрібного модуля M, сигналом RM лічильник заповнюється нулями, а з надходженням наступних імпульсів на вхід C цикл лічби повторюється.

Рисунок 9.2 – Програмовні недвійкові лічильники

Особливості проектування програмовного лічильника такого типу розглянемо на прикладі змінюваного модуля лічби M = 5 і M = 7. За максимальним модулем M = 7 вибираємо розрядність лічильника n =3, а за кількістю модифікацій модуля – розрядність керувального коду. У прикладі достатньо обмежитися однорозрядним керувальним кодом m: за його значення m = 0 програмуємо модуль на величину M = 5, а за значення m = 1 – на величину M = 7. Якщо кількість модифікацій модуля не перевищує чотирьох, вибираємо дворозрядний керувальний код m1m0, якщо восьми – трирозрядний код m2m1m0 і т. д.

Аналогічно рис. 9.1,б складаємо перемикальну таблицю (рис. 9.2,б), в якій зазначаємо, що лічильник скидається сигналом RM = 1, коли він опиняється в проміжних станах Q2Q1Q0 = 5 при m = 0 та Q2Q1Q0 = 7 при m = 1. Також позначаємо десяткові значення наборів змінних і = mQ2Q1Q0, за якими будуємо діаграму термів (рис. 9.2,в), відтак мінімізуємо функцію, застосовуючи для спрощення редукцію

![]() ,

(9.3)

,

(9.3)

та складаємо схему (рис. 9.2,г). Затримка комбінаційної частини зазвичай достатня для надійного заповнення нулями лічильника (рис. 9.2,д), але, у разі потреби, імпульси скидання розширюють, наприклад, на кшталт рис. 9.1,в.

На основі трирозрядного двійкового лічильника можна створити програмовний лічильник з модулем лічби M = 2 ... 8 із застосуванням керувального коду m2m1m0 шляхом узагальнення (9.3):

![]() ,

(9.4)

,

(9.4)

отже, аналогічно і для лічильника довільної розрядності.

Слід враховувати, що під час примусового скидання виникають проміжні стани лічильника, тому вихідний код можна знімати після закінчення перехідного процесу його усталення. Цей недолік усувають в програмовних ІС шляхом модифікації структури лічильника. Принцип такої модифікації розглянемо на прикладі перетворення двійкового лічильника за основною схемою на D-тригерах (див. [2], рис. 9.3,б) у лічильник з програмовним модулем лічби М = 2 ... 8.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.