• Interactive Mode

• In the Interactive Mode, Active-HDL acts as a slave application for Debussy and can be controlled directly from the Debussy GUI. Debussy sends commands to Active-HDL and reads simulation data from it.

• Using the Interactive Mode requires some initial setup, such as compiling the project in Active-HDL, adding a PLI application and preparing the debussy.rc file (templates are available).

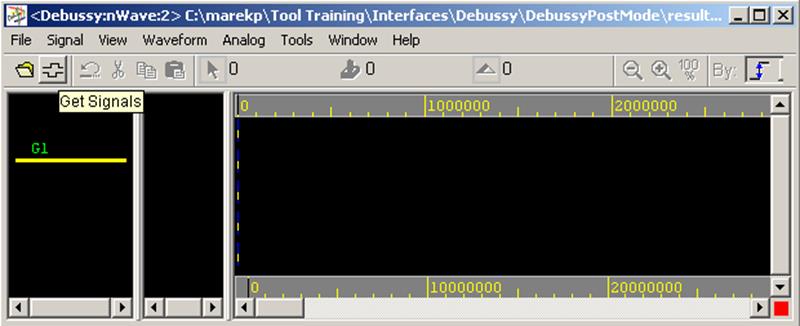

12.1a Debussy & Active-HDL

in post-processing mode

• Dumping FSDB databases can be controlled either directly from VHDL source code or with macro commands.

• To dump FSDB databases directly from VHDL code, declare the aldec library and use the package fsdb_wrapper:

library aldec;

use aldec.fsdb_wrapper.all;

• Debussy FSDB procedures (tasks) can be placed inside any process,

FSDB_DUMP:

process

begin

fsdbDumpfile("simdata.fsdb");

fsdbDumpvars(0, "");

wait;

end process;

12.1b Debussy & Active-HDL

in post-processing mode

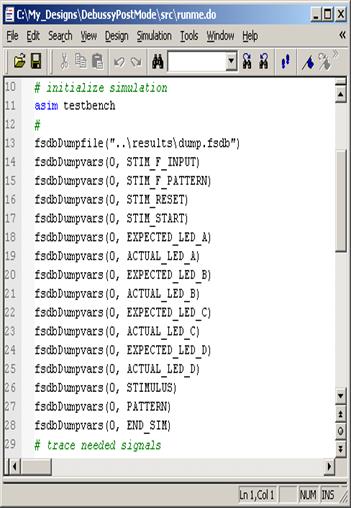

• If you do not want to modify your VHDL source code, you can dump FSDB databases using macro commands. The commands can be placed in macros or typed in the Console window after initializing the simulation process.

asim

testbench

fsdbDumpfile("simdata.fsdb")

fsdbDumpvars(0, "")

run -all

• Simulation data is automatically flushed to the FSDB database when simulation is finished with the endsim command.

12.1c Debussy & Active-HDL

Sample Design

• Open Design “DebussyPostMode”

•  Run

macro runme.do

Run

macro runme.do

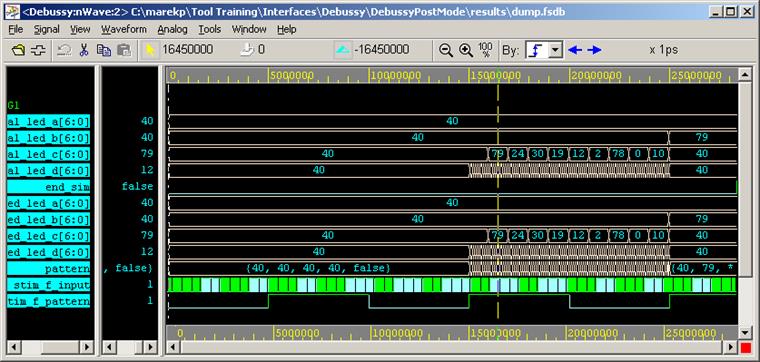

12.1d Debussy & Active-HDL

Sample Design

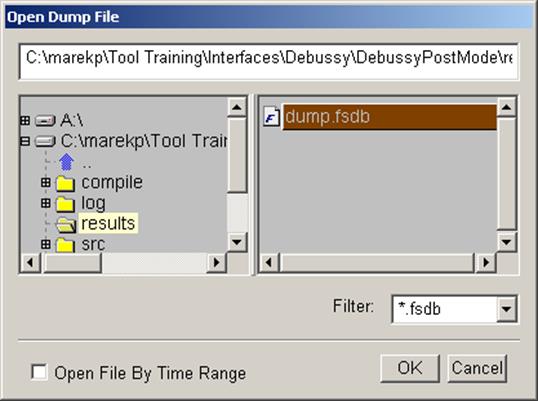

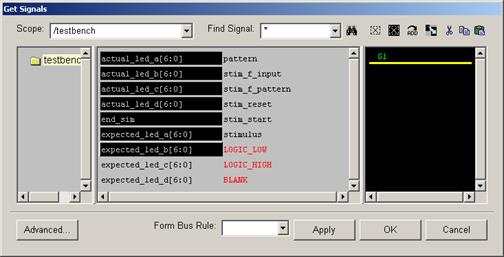

12.1e Debussy & Active-HDL

Sample Design

Choosing FSDB File.

Choosing signals.

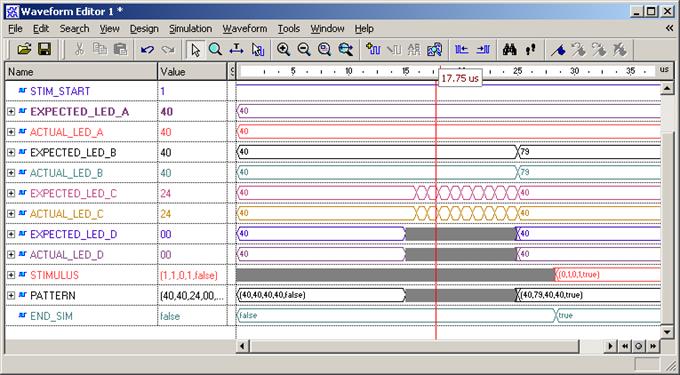

12.1f Debussy & Active-HDL

Sample Design

Debussy & Active-HDL

Waveforms

12.2 Denali

• Active-HDL supports memory models distributed by the Denali software.

• Denali models can be instantiated in Verilog designs only.

• Memory models communicate with Active-HDL via a PLI library.

• The PLI library must be built by the user.

• PLI tasks to control memory models can be placed directly in the Verilog code or called directly from the Console window.

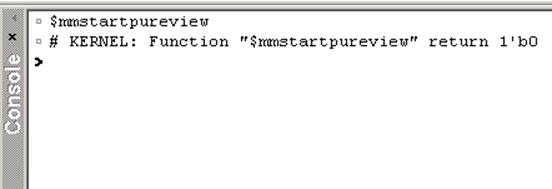

• To display the PureView memory viewer after initializing the simulation process, type $mmstartpureview in Console.

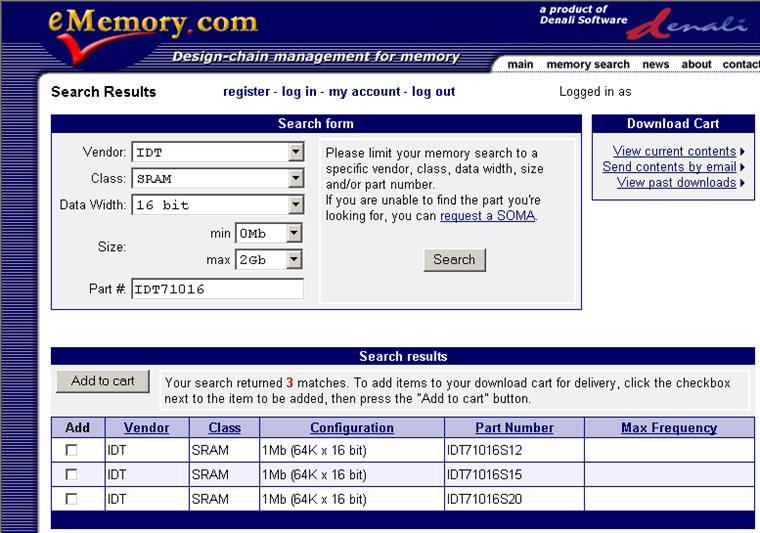

12.2a Denali Sample Design

Obtaining memory description file

• Memory model description file are available on eMemory.com.

Step #1:

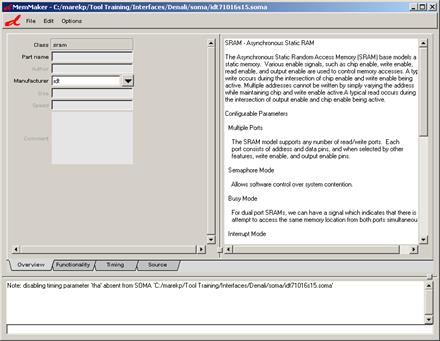

Obtain SOMA file with description of SRAM memory IDT71016.

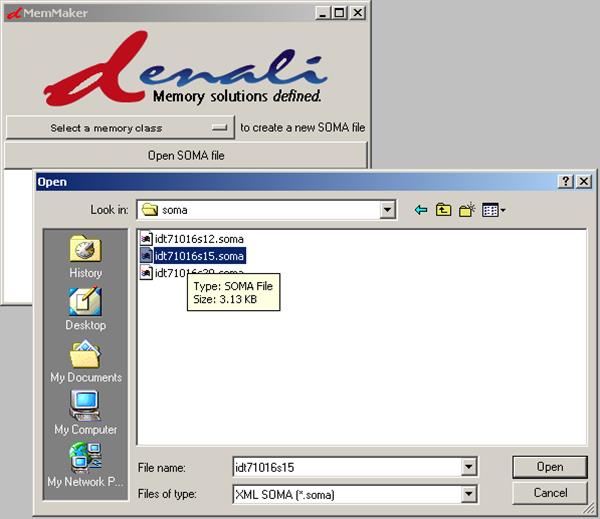

12.2b Denali Sample Design

Creating Verilog source

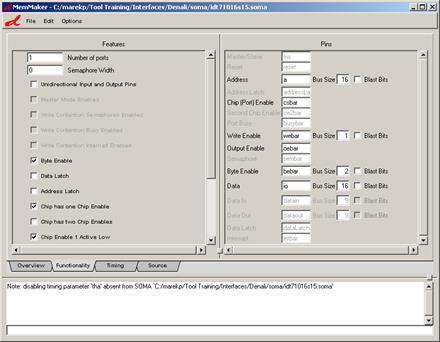

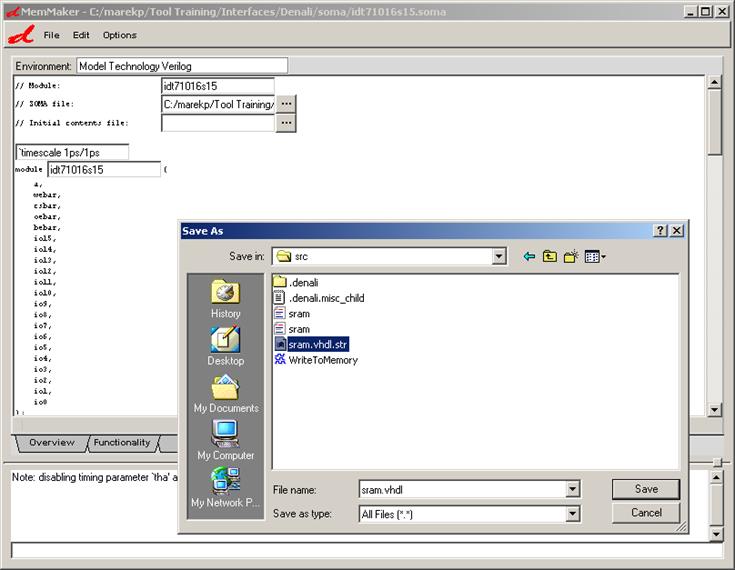

• Step #2 : Load SOMA file into MemMaker from Denali.

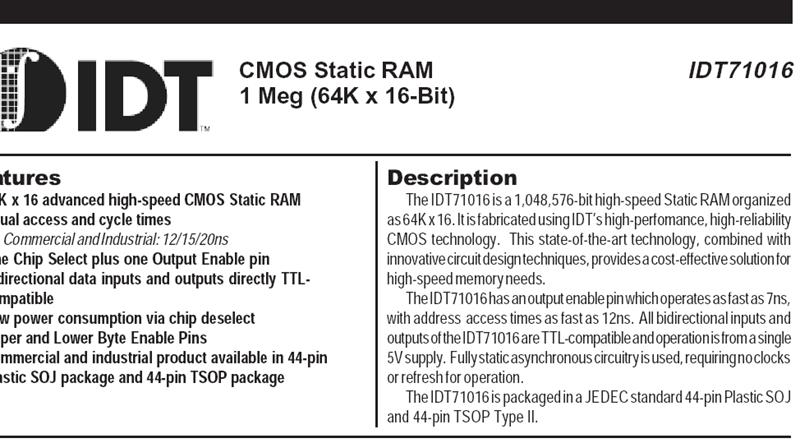

12.2c Denali Sample Design

Creating Verilog source

• Step #3 : Configuring parameters for memory model.

12.2d Denali Sample Design

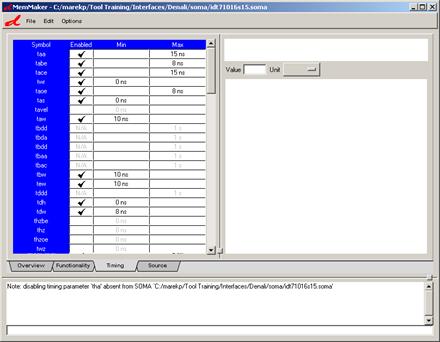

Creating Verilog source

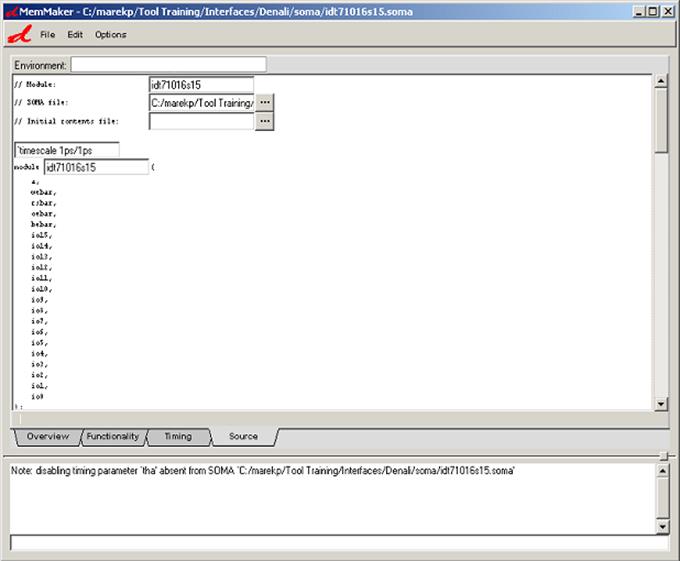

• Step #4 : Generating Verilog file for memory model - entity & architecture.

12.2e Denali Sample Design

Creating Verilog source

• Step #5 : Saving Verilog file.

12.2f Denali Sample Design

Adding VHDL file to design

• Step #6 : After adding the source file, we can compile it.

Memory models communicate with Active-HDL via a PLI library (denali.dll) that

12.2g Denali Sample Design

Initializing simulation

• Step #7 : After simulation initialization we have access to memory interface.

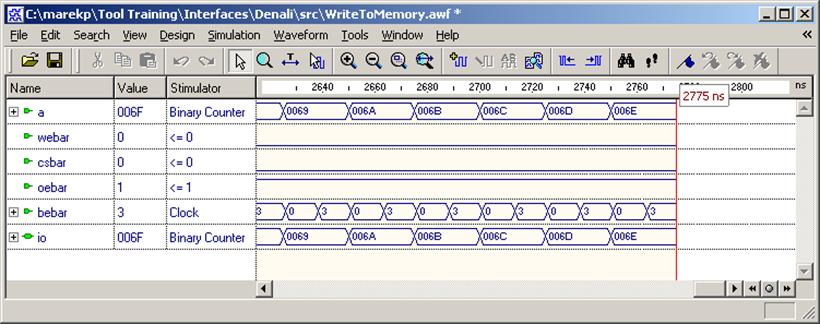

12.2h Denali Sample Design

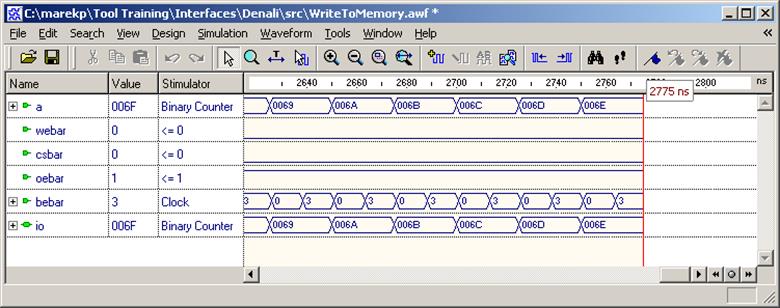

Writing data to memory

• Step #8 : We can prepare stimulators and write data to memory…

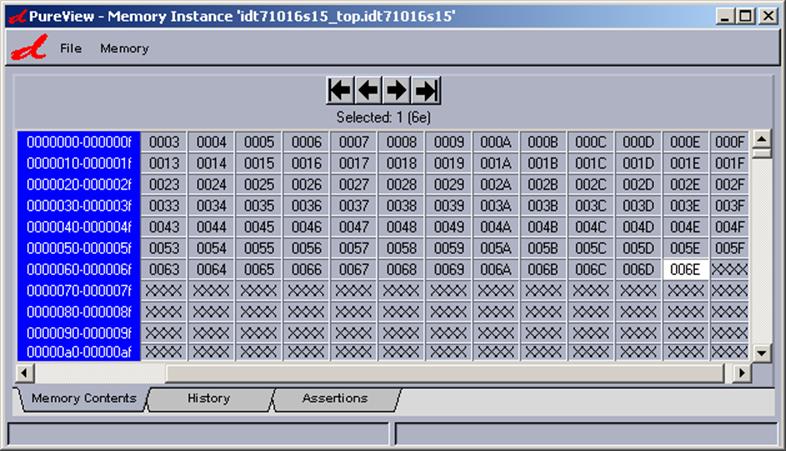

• Step #9 : We can also see the contents of memory by using $mmstartpureview task…

12.2i Denali Sample Design

Choosing memory to view

• Step #10 : After choosing memory instance we will see memory contents …

12.2j Denali Sample Design

Memory view in Denali “PureView”

12.3 SWIFT

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.