1.6 Ref. F Using Text Structure

• To take advantage of the generated code structure you can click on the buttons to collapse or expand groups of HDL statements.

• You can also create your own structures by grouping selected statements. To do this select a portion of the code and click the button.

• To revert to the original document layout, click the button. This will remove the generated structure automatically

1.7 Compiling the Design

Active-HDL allows you to compile design source files in several manners.

•

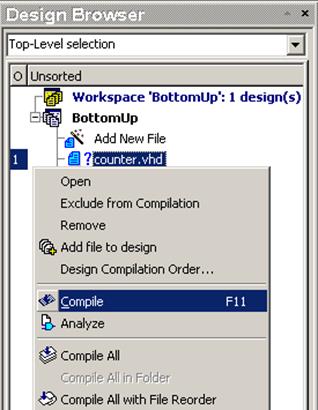

Source files can be compiled individually by

choosing the Design|Compile command

or clicking the toolbar button.

•

All source files can be compiled in one pass

according to the order set in Design Compilation Order (Design |

Design Compilation Order). To do this

select the Design|Compile All command

or click the button.

•

All source files can be compiled in one pass

with the prior reorder. The files are reordered so as to ensure the proper

order of analysis.

To do this, select the Design|Compile All with File Reorder command or

click the button.

1.7 Ref. A Compilation Status

Each source file can have one of the following statuses, denoted with additional markers placed on file icons in the Design Browser window.

![]() Errors occurred during the last compilation

Errors occurred during the last compilation

![]() Warnings occurred during the last compilation

Warnings occurred during the last compilation

![]() Not compiled or modified after the last

compilation

Not compiled or modified after the last

compilation

![]() Successfully compiled

Successfully compiled

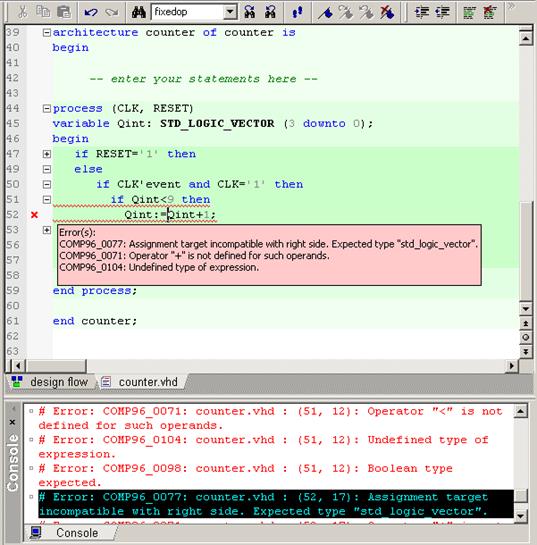

1.7 Ref. B Tracking Errors

• You can easily track any errors in the HDL Editor window (underlined in red).

• The Console window displays all errors with short descriptions and takes you directly to them by double-clicking the particular error message. Moreover, the line is marked with a red x

• .

• If you rest the cursor over the underlined line, a short error description(s) will appear.

• You can correct all errors and recompile file.

1.8 Instantiating Components

Active-HDL allows you to work with multiple-file projects.

You can then create required models in separate files and verify them individually instead of placing them in one large design file.

• By creating a top-level entity, you can test the functionality of the entire design. To do this, you must instantiate the components of the design.

• Component instantiation is like plugging a hardware component into a socket in a board.

1.8 Ref.A Instantiating Components

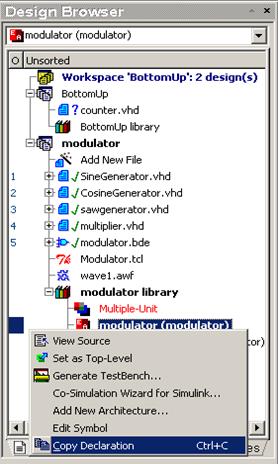

Active-HDL provides a utility to speed up a component instantiation. You can copy a component declaration from the working library or a library in the Library Manager window.

• Expand the library contents in the Design Browser and copy the declaration pressing Ctrl+C keys or use the Copy Declaration option from the pop-up menu.

• Go to the HDL Editor window and paste the declaration pressing Ctrl+V keys or using the Paste option from the pop-up menu.

Note: This will only copy the component declaration. You will have to map the ports and generics of the entity by yourself.

1.9 Creating State Machines

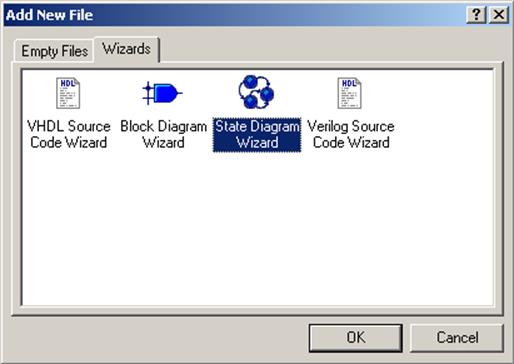

• To create a state machine, double-click the Add New File icon in the Design Browser window.

• Switch to the Wizards tab and choose State Diagram Wizard.

• Run the wizard pressing the OK button.

For further information on using the State Machine Wizard refer to the Course 2 – Top-Down Design Methodology

1.10 Creating Block Diagrams

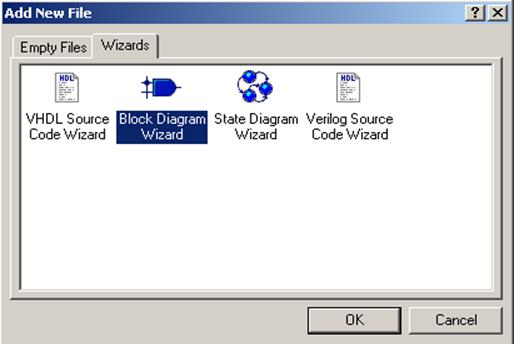

• To create a block diagram, double-click the Add New File icon in the Design Browser window.

• Switch to the Wizards tab and choose Block Diagram Wizard.

• Run the wizard pressing the OK button.

For further information on using the Block Diagram Wizard refer to Course 2 – Top-Down Design Methodology

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.