3.39 Using Source Control

If you want to make any changes to your source file(s), you must first check-out the file(s) from the Source Revision Control database.

When you Check-out a file, the Source Revision Control system places a “writeable” copy in your working folder. The source file that is checked-out may not be checked out by anyone else (unless the preferences of your Source Revision Control system have been changed to allow multiple checkout operations).

You can check out a single file, a set of files, or all sources in a project depending on their status in a database.

3.40 Using Source Control

After you have checked out a file or group of files, the following options are available:

• Check-In

You can update your file and store your changes in the current Source Revision Control database project.

• Undo Check-Out

You can undo the Check-Out operation and cancel your changes both in the Source Revision Control database project and in your design working folder. The sources return to the state they were before you checked them out.

3.41 Using Source Control

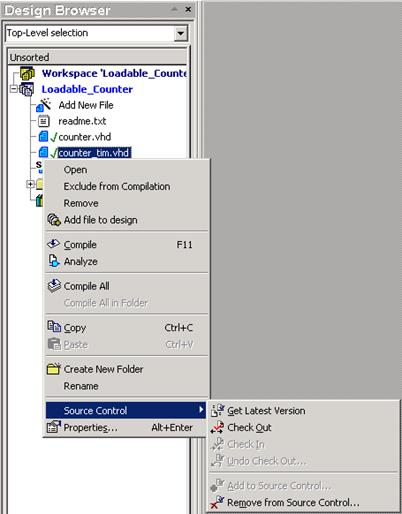

To Check-out single or multiple files and folders from the Source Revision Control database:

• Select the source(s) you want to Check-out from the Source Revision Control database.

• Invoke the Check Out command from the Source Control sub- menu.

• Click OK to Check-out the sources to the Source Revision Control database

3.42 Using Source Control

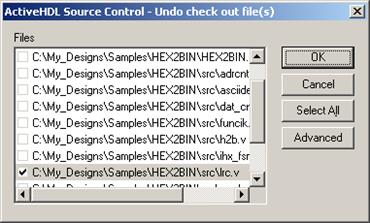

To Undo Check-out single or multiple files and folders from the Source Revision Control database:

• Select the source(s) for which you want to Undo the check out operation

• Invoke the Undo Check Out command from the Source Control sub-menu

• Click OK to Undo Check Out

the sources from the Source

Revision Control database

3.43 Using Source Control

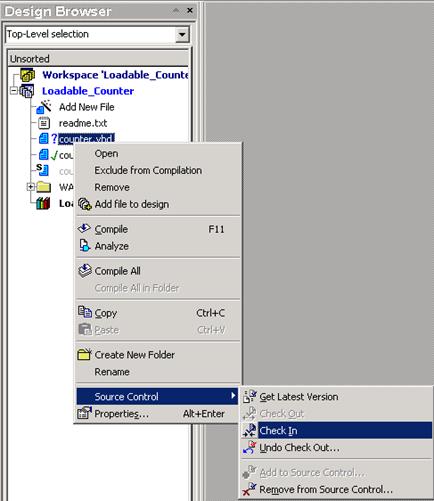

To Check-in single or multiple files and folders from the Source Revision Control database:

• Select the source(s) you want to Check-in from the Source Revision Control database.

• Invoke the Check In command from the

Source Control

sub- menu

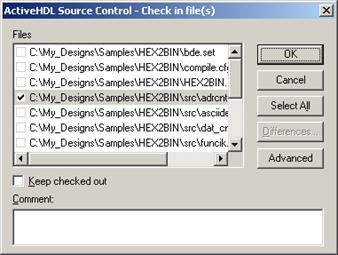

• Click OK to Check-in the

sources to the Source

Revision Control database

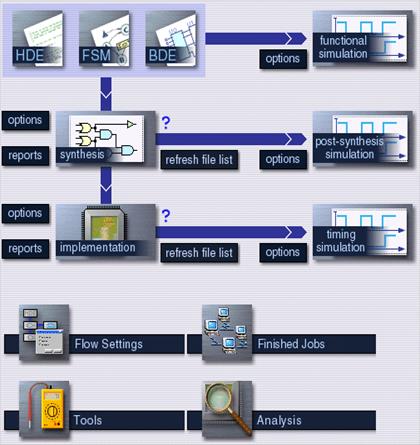

3.44 Design Flow Manager

Support for new synthesis and implementation tools

• Synthesis tools:

- Synopsys FPGA Express

- Synopsys FPGA Express(Xilinx OEM)

- Synopsys FPGA Compiler II

- Synopsys FPGA Express (Innoveda OEM/ Viewlogic OEM)

- Synplicity Synplify 7.x

- Synplicity Synplify Pro 7.x

- Xilinx ISE 5.x/6.x XST VHDL/Verilog

- Xilinx ISE 5.x/6.x Synthesis&Implementation

- XST VHDL

- XST Verilog

- Exemplar Leonardo

- Exemplar flow for Chip Express

- Exemplar Leonardo (Atmel OEM)

- Cypress Synthesis&Implementation

- Quartus Synthesis&Implementation

• Implementation tools:

- Altera Maxplus

- Xilinx® ISE 4.x/5.x/6.x

- Xilinx® WebPack 3.3/4.x/5.x/6.x

- Xilinx® Foundation 3.3/4.x

- Xilinx® Alliance 3.3/4.x

- Quicklogic™ Implementation

- Actel Designer™

- Actel Designer™ v5.0

- Atmel Figaro IDS 7.5

- Quartus Implementation

- Cypress Implementation

- Lattice ispLEVER™

- Triscend FastChip

3.45 Design Flow Manager

- Collaboration with Server Farm

• It allows designers to put in the queue their simulation, synthesis, and implementation tasks.

• Selecting this checkbox, you will be able to run the synthesis process on a server-farm computer.

• The list box next to the Use Server Farm checkbox allows you to choose the location (Farm Controller) where your design sources will be sent to process.

• The Farm Controller is also a computer where the results of synthesis are stored until you download them to your computer.

• The download process is equivalent to the MOVE operation

4. Design Verification

HDL Debugging

Course 4

4. Debugging

Active-HDL provides several mechanisms for efficient HDL code debugging and viewing design interconnects:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.