Для МПС характерна трехшинная организация ША, ШД, ШУ. Это внешние по отношению к МП шины. Возможны разные организации шин: одна двухнаправленная ШД или две однонаправленных (одна из которых является входной для МП, другая выходной). МП в заданной последовательности выбирает команды из ПЗУ и выполняет их. Для выбора команд МП последовательно устанавливает на ША адреса ( номера ) ячеек памяти. Код команды, выбранный из заданной ячейки, вводится в МП по ШД и вызывает выполнение соответствующей операции в МП.

Для хранения промежуточных результатов или для ввода на обработку совокупности исходных данных имеется память данных – ОЗУ, которая в отличие от ПЗУ должна работать как в режиме чтения, так и в режиме записи информации. Адреса ячеек для записи данных формируются МП и передаются в блок памяти по ША. Обмен информацией между МП и ОЗУ производится по ШД словами, разрядность которых равна разрядности ШД.

Ввод исходной информации на обработку и вывод результатов осуществляется через блок интерфейса (И), который служит для сопряжения сигналов МПС и внешних устройств.

В качестве внешних устройств (ВУ) могут использоваться любые ВУ из состава микро – ЭВМ: дисплеи, печатающие устройства, накопители на магнитных дисках, модемы и т.д. Однако при использовании МПС непосредственно в блоках РЭА, роль ВУ ввода играют АЦП, преселекторы (устройства предварительной обработки информации), обнаружители сигналов и т.п. ВУ вывода – индикаторы, исполнительные устройства, блоки передачи и т.п.

Для синхронизации МПС в целом используют генератор тактовых импульсов (ГТИ). Период следования импульсов ГТИ является машинным тактом.

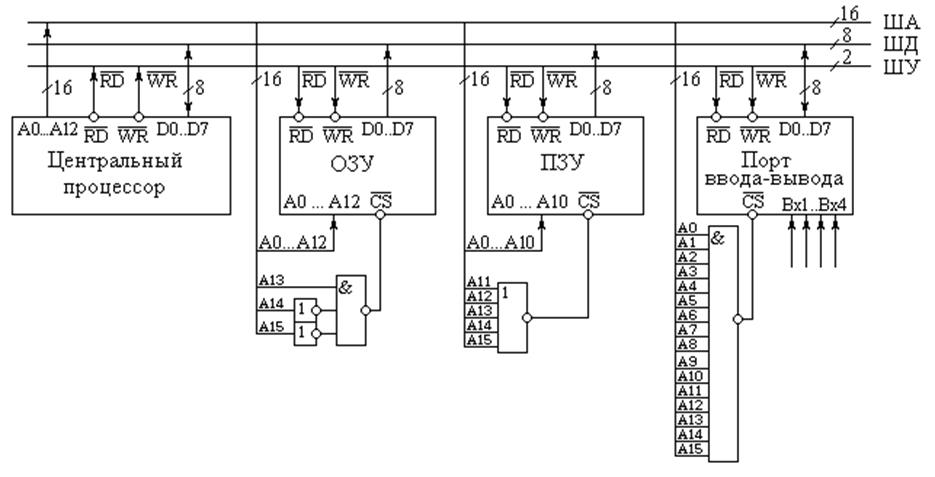

Системная шина процессора (МП) – совокупность ША, ШД, ШУ. Она предназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы. Схема восьмиразрядной МПС приведена на рисунке 7.13.

Рисунок 7.13. Структурная схема восьмиразрядной МПС

На этом рисунке обозначено:

· А – адресные линии;

· D – линии данных;

· CS – вход выбора кристалла. Если CS = 0, то микросхема работает;

· RD – сигнал чтения;

· WR – сигнал записи.

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных даже при реализации Гарвардской архитектуры.

В понятие шины вкладывают различный смысл при рассмотрении различных вопросов. В простейшем случае под понятием шина подразумевают совокупность проводников, по которым передаётся двоичная информация. При этом по каждому проводнику передаётся отдельный двоичный разряд. Информация может передаваться в одном направлении, что чаще всего бывает для шины адреса или шины управления или в различных направления как это обычно бывает для шины данных. По шине данных информация передаётся либо к процессору, либо от процессора в зависимости от операции записи или чтения, которую в данный момент осуществляет процессор.

В любом случае все сигналы, необходимые для работы системной шины формируются микропроцессором. Иногда для увеличения скорости обмена информацией функции управления системной шины берёт на себя отдельное устройство (например, контроллер прямого доступа к памяти или сопроцессор). При этом, должен быть обеспечен интерфейс, то есть обеспечены условия согласования устройства с системной шиной по уровням напряжений, длительности фронтов передаваемых сигналов, способам кодировки, синхронизации, контроля, типам используемых разъёмов, последовательности и скорости передаваемых сигналов. На интерфейсы существуют стандарты. Их много, но наличие интерфейса позволяет разрабатывать внешние устройства не зависимо от типа микропроцессорной системы. При подключении различных устройств к системной шине возникает вопрос - как различать эти устройства между собой? Для этого каждому внешнему устройству (ячейке) придается индивидуальный адрес. Так как обращение производится к каждой ячейке индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством и адресного пространства микропроцессорной системы в целом.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.