В некоторых случаях возможно использование безадресных команд, когда подразумеваются адреса операндов и результата операции.

Наиболее логичны и естественны трёхадресные команды, но они недопустимо длинные. Кроме того, в качестве операндов используются результаты предыдущих операций, хранимых в регистрах машины. Поэтому выполняемая операция, приобретает характер одно – или двухадресной. В современных ЭВМ применяют одно, двухадресные команды и их модификации.

7.2 Типовая структура обрабатывающей части микропроцессора

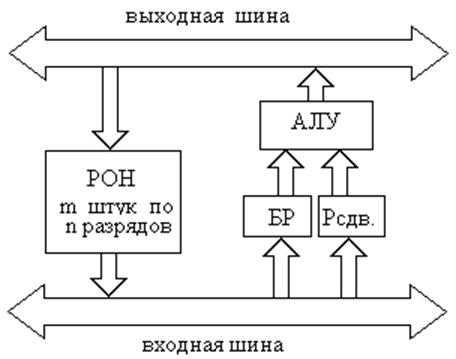

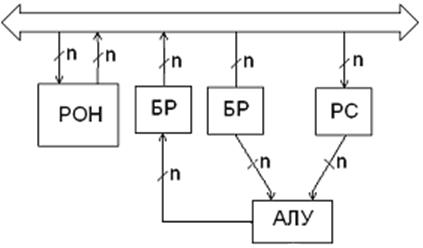

Основой любого МП является арифметико-логическое устройство и набор регистров общего назначения (РОН), часто называемый сверхоперативным запоминающим устройством. В РОН хранятся слова подлежащие обработке и результаты обработки. Эта структура приведена на рисунке 7.3.

Рисунок 7.3 – Обрабатывающая часть МП без управляющих цепей

В микропроцессоре содержимое любого РОН может быть передано на буферный регистр (БР) и регистр сдвига (Рсдв.). АЛУ выполняет арифметические и логические операции над содержимым этих регистров, а результат этих операций записывается в любой из РОН.

В этой системе возможно:

- передача данных из одного РОН в другой путем пересылки слова транзитом через БР и АЛУ;

- увеличение или уменьшение на единицу содержимого любого РОН и АЛУ и засылки результата в тот же или другой регистр;

- сдвиг содержимого любого РОН путем передачи через Рсдв. и АЛУ в тот же РОН.

Очевидно, что для выполнения этих и других операций на АЛУ, РОН, БР и Рсдв. должны подаваться определенные управляющие сигналы. Причем, важное значение имеет их распределение во времени.

Например, для передачи слова из одного РОН в другой требуется два такта(операции):

такт 1 – выборка содержимого РОН и его прием в БР;

такт 2 – запись информации, переданной на вход РОН через АЛУ.

Таковые сигналы поступают от тактового генератора, причем, максимально возможная частота, а значит и время выполнения одной операций будут определяться задержкой сигналов в различных элементах схемы.

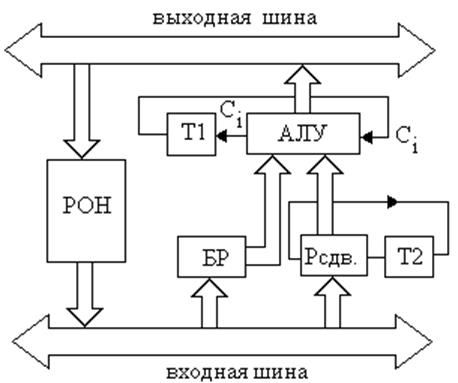

В ряде случаев сигнал арифметического переноса из АЛУ и выходной бит регистра сдвига должны быть сохранены для последующих операций. Это выполняется с помощью двух D - триггеров. Тогда обрабатывающая часть МП принимает вид, приведенный на рисунке 7.4.

Рисунок 7.4 – Обрабатывающая часть МП с триггерами Т1 (хранения переноса)

и Т2 (хранения сдвига)

В этом случае становятся возможными операции над словами с разрядностью большей, чем разрядность шин, АЛУ, РОН и других регистров.

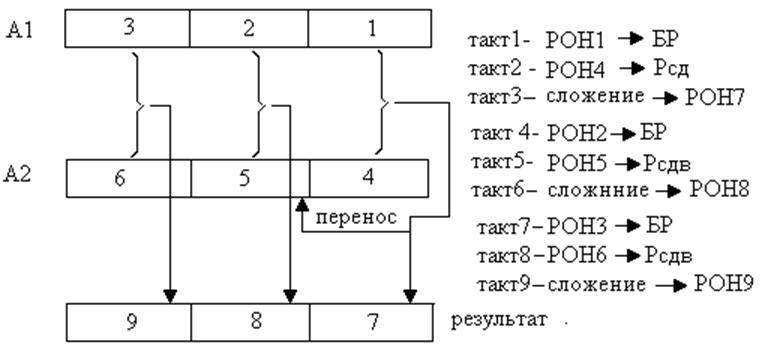

Например, при 4-х разрядной организации этих узлов можно выполнить обработку 12 разрядных слов, для хранения каждого из которых в блоке РОН отводится три регистра. Но для их обработки уже требуется три цикла обработки четырехразрядного слова. Схематично это показано на рисунке 7.5.

Рисунок 7.5 – Сложение 12- разрядных операндов

при 4-х разрядной организации МП

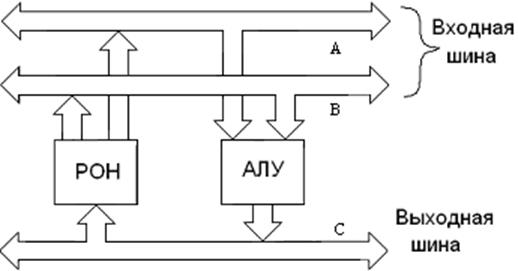

Рассмотренная структура с двумя шинами данных (входной и выходной) не является единственно возможной. В различных МП используются 1,2 или 3 внутренних шины. Их число существенно влияет на структуру и характеристики МП. На рисунке 7.6 показана трёхшинная организация МП.

Рисунок 7.6 – Трёхшинная организация МП

В такой системе возможно выполнение арифметических и логических операций за один такт. Кроме высокого быстродействия здесь отсутствуют буферные регистры. Недостаток: большая площадь, занимаемая на кристалле.

При одношинной организации МП (рисунок. 7.7) обязательно наличие двух или трёх БР.

Рисунок 7.7 – Одношинная организация МП

Эта структура занимает на кристалле наименьшую площадь. Наличие БР увеличивает функциональные возможности этой системы, но у неё низкое быстродействие. Арифметические и логические операции выполняются не менее чем за 2 или 3 такта.

7.3 Устройство управления в МП

Устройство управления МП должно выполнять две основные функции: выборку команд программы в нужной последовательности и обработку полей команд.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.