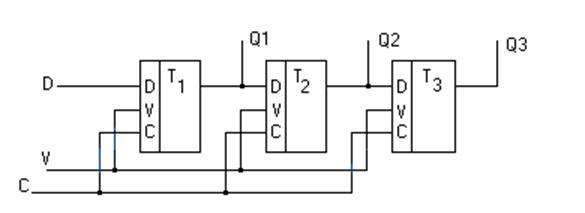

Поэтому, регистры сдвига удобно выполнять на DV-триггерах (рис. 5.17). На вход V подают сигнал микрооперации сдвига.

Рисунок 5.17 – Регистр сдвига на DV – триггерах

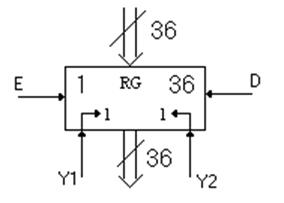

Регистр сдвига на операционной схеме обозначают так (рис. 5.18)

Рисунок 5.18 – Регистр сдвига на операционной схеме

На этом рисунке обозначено: Y1 - микрооперация сдвига вправо на 1 бит; Y2 - микрооперация сдвига влево на 1 бит; Д, Е - дополнительная информация, которая помещается в освобождающиеся разряды. Тогда происходит составление нового слова на регистре

Y1: P1: = сдв ЛП (1)

P2 I E ![]()

Y2: P2: = сдв ЛЛ (1) P2 I D

Микрооперация составления нового слова называется конкатенацией.

Регистры сдвига широко используются для организации последовательных АЛУ, преобразований кодов и выпускаются в виде отдельных микросхем

( К155ИР1, К155ИР11 и др.).

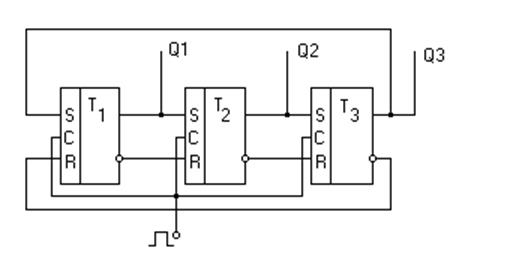

Если вход и выход регистра сдвига соединить между собой, то код будет непрерывно циркулировать по замкнутому контуру, получается так называемый динамический регистр. Возьмём трёхразрядный регистр сдвига (рис. 5.19).

Рисунок 5.19 – Динамический регистр

Пусть в исходном состоянии на регистре записан код 1 0 0 (такт № 0). В каждом последующем такте эта единица будет перемещаться (рис.5.20)

|

Такт |

Q1 |

Q2 |

Q3 |

tцсх<tцц |

tцсх>tцц |

||||

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

||||||

|

2 |

0 |

0 |

1 |

0 |

0 |

1 |

|||

|

3 |

1 |

0 |

0 |

||||||

|

4 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

5 |

0 |

0 |

1 |

||||||

|

6 |

1 |

0 |

0 |

1 |

0 |

0 |

|||

|

7 |

0 |

1 |

0 |

||||||

|

8 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

||||||

|

10 |

0 |

1 |

0 |

0 |

1 |

0 |

|||

|

11 |

0 |

0 |

1 |

||||||

|

12 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

13 |

0 |

1 |

0 |

||||||

|

14 |

0 |

0 |

1 |

0 |

0 |

1 |

|||

|

15 |

1 |

0 |

0 |

||||||

|

16 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

17 |

0 |

0 |

1 |

||||||

|

18 |

1 |

0 |

0 |

1 |

0 |

0 |

|||

|

19 |

0 |

1 |

0 |

||||||

Рисунок 5.20 – Движение кода в динамическом регистре

Видно, что код на регистре повторяется через n-тактов, где n = 3 - число разрядов регистра.

Существуют два понятия:

1) Период циркуляции кода на регистре. Он равен числу разрядов (tцц = n).

2) Период цикла схемы - это время, через которое код считывается из регистра (t цсх).

В зависимости от соотношения tцц и tцсх возможны три режима работы:

1) tцц = tцсх - это режим хранения информации.

2) tцсх < tцц - режим сдвига влево (регистр со сдвигом влево).

3) tцсх > tцц - регистр со сдвигом вправо.

Получился универсальный регистр, но быстродействие его невысокое.

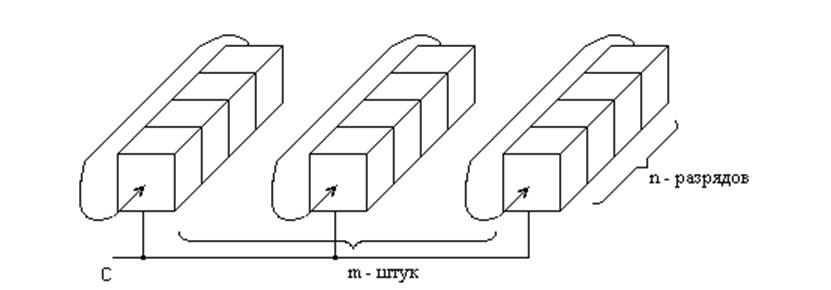

Динамические n – разрядные регистры соединяются в блоки по m штук (как показано на рис. 5.21) и записывают в них слова “поперёк”. Всего можно записать n штук m – разрядных слов. Эти слова появляются в некотором сечении регистров через время равное n тактов. Получили, так называемую, регистровую память или цифровую линию задержки (ЦЛЗ).

Рисунок 5.21 – Цифровая линия задержки

Для этих целей специально выпускаются регистры. Например, микросхема К144ИР3 – регистр на 64 бит (задержка на 64 такта).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.