Сложность корпусов с кварцевым окошком и малое количество циклов перезаписи заставили искать другие способы стирания информации из РПЗУ. Таким способом является электрическое стирание каждой ячейки. Количество циклов перезаписи для этих микросхем достигает 105 раз. Время стирания уменьшается до 10 мс.

Схема управления для микросхем с электрическим стиранием получается довольно сложная, поэтому наметились два направления развития этих микросхем:

1. ЭСППЗУ – электрически стираемые репрограммируемые

2. FLASH – с групповым электрическим стиранием

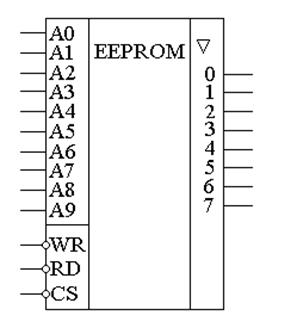

Электрически стираемые ППЗУ дороже и имеют меньший объем хранимой информации, но зато позволяют перезаписывать каждую ячейку памяти отдельно. В результате эти микросхемы обладают максимальным количеством циклов записи - стирания. Область применения электрически стираемых ППЗУ - хранение данных, которые не должны стираться при выключении питания. К таким микросхемам относятся микросхемы 558РР1, 558РР3, 558РР23 и др. Электрически стираемые ППЗУ обозначаются на принципиальных схемах как показано на рисунке 6.7.

Рисунок 6.7 - Обозначение электрически стираемого постоянного

запоминающего устройства на принципиальных схемах

В последнее время наметилась тенденция уменьшения габаритов ЭСППЗУ за счет уменьшения количества внешних выводов микросхем. Для этого адрес и данные передаются в микросхему и из неё последовательно во времени.

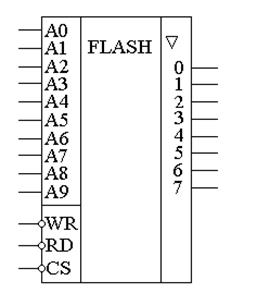

FLASH - ПЗУ отличаются от ЭСППЗУ тем, что стирание производится не каждой ячейки отдельно, а всей микросхемы в целом или блока запоминающей матрицы этой микросхемы, как это делалось в РПЗУ. Изображение FLASH – ПЗУ на принципиальных схемах приведено на рисунке 6.8.

Рисунок 6.8 - Обозначение FLASH памяти на принципиальных схемах

6.3 Оперативные запоминающие устройства

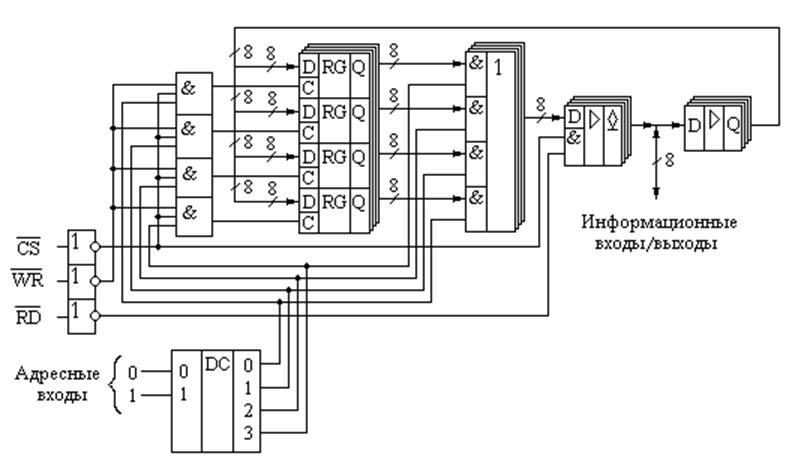

В радиоаппаратуре часто требуется хранение информации, значение которой не важно при включении устройства. Для временного хранения информации можно воспользоваться параллельными регистрами. Так как запоминаемые слова не нужны одновременно, то можно воспользоваться механизмом адресации, который применяется в ПЗУ. Рассмотрим такие адресные ОЗУ.

Схемы, в которых в качестве запоминающей ячейки используется триггер (или регистр) называется статическим ОЗУ (SRAM), т.к. информация в ней сохраняется все время, пока к микросхеме подключено напряжение питания. В схемах ОЗУ присутствуют две операции: операция записи и операция чтения. Для записи и чтения информации можно использовать две различные шины данных, но чаще используется одна и та же шина данных. Это позволяет экономить выводы микросхем, подключаемых к этой шине и легко осуществлять коммутацию сигналов между различными устройствами.

Схема статического ОЗУ приведена на рисунке 6.9.

Рисунок 6.9 - Структурная схема статического адресного ОЗУ

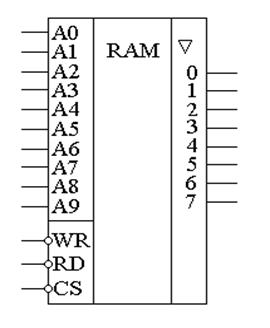

Информационные входы и выходы в этой схеме объединены при помощи шинного формирователя в двунаправленную шину. Естественно, что схемы реальных ОЗУ будут отличаться от приведенной, но она позволяет понять, как работает реальное ОЗУ статического типа. Условное изображение ОЗУ на принципиальных схемах приведено на рис. 6.10

Рисунок 6.10 - Изображение ОЗУ на принципиальных схемах

Сигнал записи WR разрешает записать сигналы, присутствующие на информационных входах во внутреннюю ячейку ОЗУ. Сигнал чтения RD позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. В приведенной схеме невозможно одновременно производить операцию записи и чтения, но это и не нужно.

Конкретная ячейка (регистр) микросхемы, в которую будет записываться информация, выбирается при помощи двоичного кода - адреса ячейки. Объем памяти микросхемы это количества ячеек, содержащихся в ней. Количество адресных линий однозначно определяется количеством ячеек памяти. И наоборот, количество ячеек памяти можно определить по количеству адресных линий. Для того, чтобы определить количество ячеек памяти, достаточно возвести число 2 в степень, равную количеству адресных линий: М = 2 n .

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.