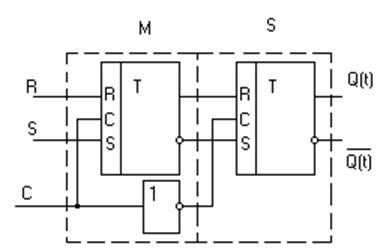

Если сигнал С=1, то первая ступень находится в режиме приема информации, а вторая - в режиме хранения, так как сигнал синхронизации на её входе равен нулю. Если С=0, то первый триггер переходит в режим хранения, а второй - в режим приема информации и копирует состояние первого триггера. Именно в этот момент информация появляется на выходе триггера (Q).

Рисунок 4.32 – Двухтактный RS – триггер

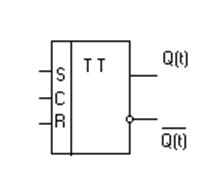

Двухтактный триггер обозначается двумя буквами Т (рис. 4.33).

Рисунок 4.33 – Изображение двухтактного RS – триггера

Зачем нужны

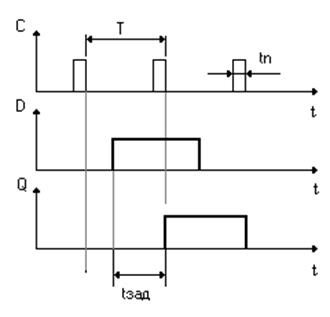

двухтактные триггеры? Во-первых, они имеют высокую помехоустойчивость, а

во-вторых, с помощью двухтактного D – триггера можно задержать

сигнал на время равное периоду синхронизации (в однотактных - только на

время паузы).

Это поясняется эпюрами рис. 4.34 . ![]() .

.

Рисунок 4.34 – Задержка сигнала в двухтактном D - триггере

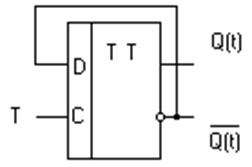

Имея двухтактный D – триггер, несложно получить асинхронный T – триггер (рис. 4.35).

Рисунок 4.35 – Асинхронный Т – триггер на основе

двухтактного D - триггера

Вообще, любой триггер можно синтезировать на любом другом типе триггера, воспользовавшись словарём переходов последнего.

4.3 Способы управления триггерами

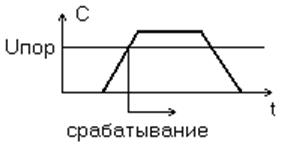

В зависимости от того, какая часть синхросигнала вызывает опрокидывание триггера, все триггеры делят на статические и динамические. Статические триггеры управляются уровнем сигнала - это потенциальные триггеры. Они опрокидываются, когда уровень синхросигнала выше некоторого порога Uпор (рис.4.36).

Рисунок 4.36 – Синхросигнал триггера

Такие триггеры

воспринимают любую информацию со своих входов, если С![]() Uпор, то есть триггер “прозрачен”

для входной информации. В некоторых случаях это неудобно, поэтому в триггерах c динамическим

управлением информация воспринимается только во время перехода синхросигнала

0

Uпор, то есть триггер “прозрачен”

для входной информации. В некоторых случаях это неудобно, поэтому в триггерах c динамическим

управлением информация воспринимается только во время перехода синхросигнала

0 ![]() 1 или наоборот. Все остальное время

информационные входы блокированы, как в двухтактных триггерах (0

1 или наоборот. Все остальное время

информационные входы блокированы, как в двухтактных триггерах (0![]() 1 прямое динамическое управление; 1

1 прямое динамическое управление; 1![]() 0 обратное динамическое управление).

0 обратное динамическое управление).

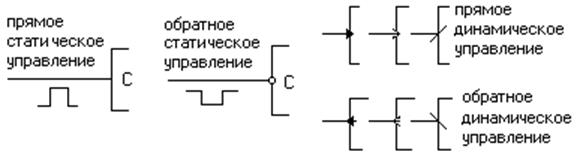

Обозначения различных синхровходов показаны на рис. 4.37:

Рисунок 4.37 – Обозначения синхровходов триггеров

Синхровход в двухтактных триггерах всегда обозначается как статический.

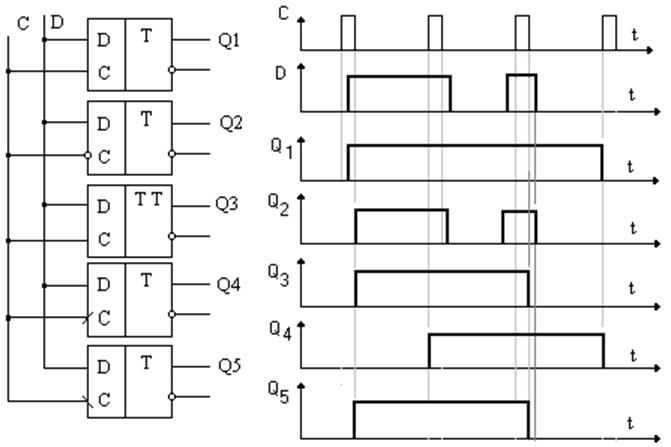

Рассмотрим влияние типа управления на выходные сигналы триггера. Возьмем пять D-триггеров с различными типами синхровходов, как показано на рис. 4.38

а) б)

Рисунок 4.38 – Влияние типа управления на выходные

сигналы D – триггера

Видно, что реакция триггера с обратным динамическим управлением и двухтактного триггера одинакова. Очевидно, что помехоустойчивость триггеров с динамическим управлением выше, чем статических. В динамических триггерах помеха может пройти на выход только, если она по времени накладывается на фронт синхроимпульса.

5 Элементы цифровых устройств

5.1 Уровни представления вычислительных устройств

Вычислительные устройства относятся к классу сложных устройств и в зависимости от минимальной неделимой единицы различают четыре уровня их представления:

1) Уровень электрических схем.

Здесь минимальной неделимой единицей является радиокомпонент (диод, резистор, конденсатор, транзистор и т.д.). Для анализа и синтеза этих схем используют дифференциальные уравнения для токов и напряжений, законы Кирхгофа. Такой уровень представления допустим, когда число компонентов не превышает 10 … 20.

2) Уровень логических схем.

Здесь минимальной неделимой единицей являются логические и запоминающие элементы, каждый из которых содержит до тысячи радиокомпонентов. Для анализа и синтеза таких схем используют язык булевой алгебры. Этот уровень описания допустим при числе элементов в пределах 200.

3) Уровень операционных схем.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.