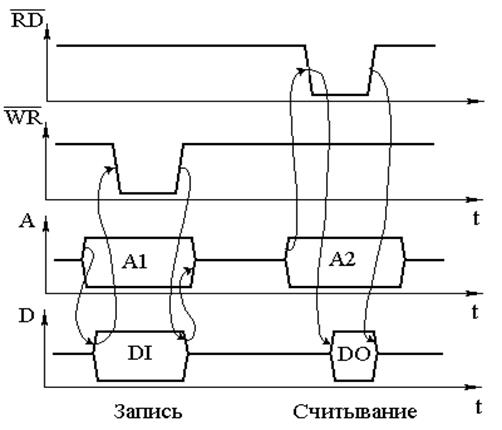

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Они имеют высокое быстродействие, простую принципиальную схему и могут работать на сколь угодно низких частотах, вплоть до постоянного тока. Кроме того, статические ОЗУ применяются для построения Кэш-памяти в универсальных компьютерах. Временные диаграммы статического ОЗУ приведены на рисунке 6.11.

Рисунок 6.11 - Временная диаграмма обращения к ОЗУ

На рисунке 6.11 стрелками показана последовательность, в которой должны подаваться управляющие сигналы. RD - сигнал чтения; WR - сигнал записи; A - сигналы выбора ячейки (так как отдельные биты в шине адреса могут принимать разные значения, то показаны пути перехода как в единичное, так и в нулевое состояние); DI - входная информация, предназначенная для записи в ячейку по адресу A1; DO - выходная информация, считанная из ячейки ОЗУ по адресу A2.

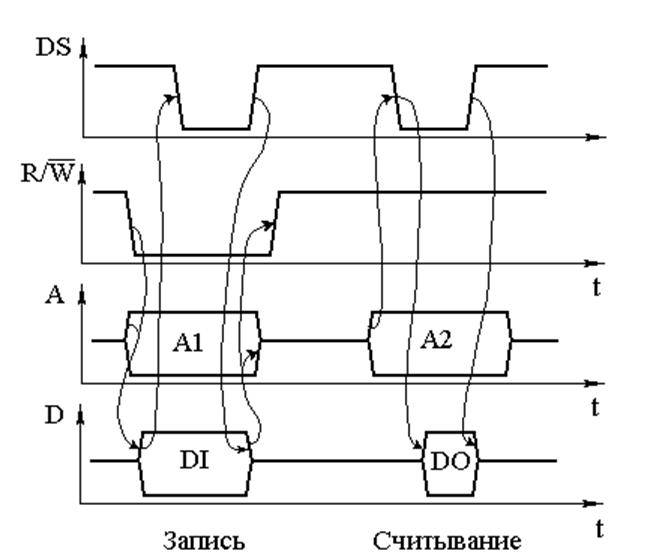

Такая временная диаграмма получила широкое распространение, но она не единственная, применяемая в микропроцессорных системах. Например, другая последовательность обмена предполагает наличие стробирующего сигнала (строба) и сигнала выполняемой операции (запись или чтение).

Временная диаграмма, поясняющая этот обмен, приведена на рисунке 6.12.

Рисунок 6.12 - Временная диаграмма обращения к ОЗУ со стробом

На этом рисунке стрелками показана последовательность, в которой должны формироваться управляющие сигналы, при этом R/W - сигнал выбора операции записи или чтения; DS - сигнал стробирования данных; A - адрес ячейки; DI - входная информация, предназначенная для записи в ячейку по адресу A1; DO - выходная информация, считанная из ячейки по адресу A2.

В качестве примера статических ОЗУ, можно назвать микросхемы КР537РУ17 (8К х8бит), К155РУ7 (1К х1бит), К132 РУ6А (16К х1бит).

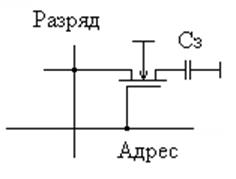

Для построения ОЗУ большого объема в качестве запоминающей ячейки применяют конденсатор – динамические ОЗУ (DRAM). Заряд ёмкости с течением времени уменьшается, поэтому его необходимо восстанавливать с периодом приблизительно 2…10 мс. Этот период называется периодом регенерации. Подзаряд ёмкости производится при считывании ячейки памяти, поэтому для регенерации информации достаточно просто считать регенерируемую ячейку памяти.

Схема запоминающего элемента динамического ОЗУ приведена на рисунке 6.13.

Рисунок 6.13 - Схема запоминающего элемента динамического ОЗУ

и его конструкция

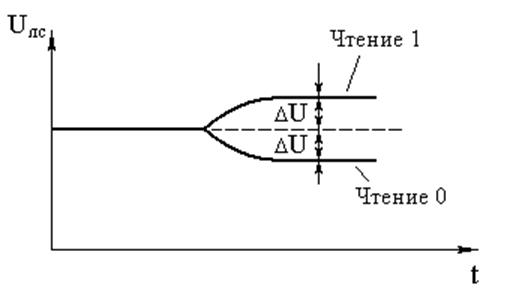

К запоминающему элементу (Сэ) подходит две линии – адресная и разрядная (линия считывания). При считывании информации на разрядной линии присутствует напряжение равное половине напряжения питания. До этого уровня заряжена паразитная ёмкость разрядной линии, которая значительно больше ёмкости запоминающей ячейки Сэ (около 0.1 пф). При считывании, Сэ либо разряжается на линию и напряжение на разрядной линии возрастает, либо заряжается от линии и напряжение на линии падает. Графики изменения напряжения при считывании информации из запоминающей ячейки приведены на рисунке 6.14.

Рисунок 6.14 - Графики изменения напряжения на разрядной линии при считывании информации из ячейки

Для регенерации первоначального напряжения в схеме применяются RS триггеры.

Особенностью динамических ОЗУ является мультиплексирование шины адреса. Адрес строки и адрес столбца передаются поочередно. Адрес строки синхронизируется стробирующим сигналом RAS (Row Address strobe), а адрес столбца - сигналом CAS (Column Address Strobe). Мультиплексирование адресов позволяет уменьшить количество выводов микросхем ОЗУ, что очень важно для микросхем с большим объёмом памяти. Изображение микросхемы динамического ОЗУ приведено на рисунке 6.15.

Рисунок 6.15 - Изображение динамического ОЗУ на принципиальных схемах

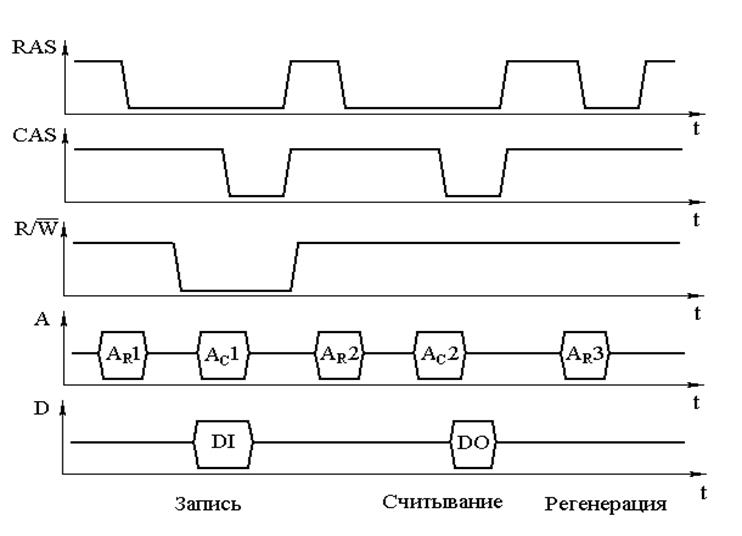

На рисунке 6.16 показаны временные диаграммы при обращении к динамическому ОЗУ

Рисунок 6.16 - Временные диаграммы при обращения к динамическому ОЗУ

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.