Проанализируем эту таблицу. Если на все управляющие входы подать низкий потенциал, то к входу сумматора будут подключены коды A и B без инверсии. В этом случае будет производиться операция суммирования. Эта ситуация отображена первыми двумя строками таблицы выполняемых операций.

Операция вычитания осуществляется второй, третьей, восьмой и девятой строкой. В этом случае один из операндов поступает на вход сумматора через блок инверторов. Правда, для получения дополнительного кода не хватает единицы, но её можно подать на вход переноса сумматора PI.

Ещё одной часто используемой операцией является увеличение числа на единицу (инкремент) или уменьшение числа на единицу (декремент). Такие операции могут быть выполнены при помощи кодов, записанных в строках четыре, семь, шестнадцать и двадцать пять.

Кроме того, схема арифметического устройства может просто передавать на выход любой из входных кодов без изменения, что позволяет осуществлять копирование данных (суммирование с константой ноль) через это устройство без дополнительных схем коммутации.

При небольшом изменении схемы такое устройство может быть преобразовано в схему, которая позволяет осуществлять не только арифметические, но и логические операции. Для этого нужно вести дополнительный коммутатор, который будет разрывать цепи переноса между разрядами. Эта управляющая цепь обычно

называется М (М – mode - режим).

Многофункциональные АЛУ выпускают в виде микросхем. Например, ИМС К531 ИП3 – четырехразрядное АЛУ. Выполняет 16 различных арифметических и логических операций над четырёхразрядными операндами и позволяет наращивать их разрядность.

В вычислителях, где входные операнды поступают по одной шине данных поочерёдно, используют АЛУ с регистрами для запоминания операндов и результата.

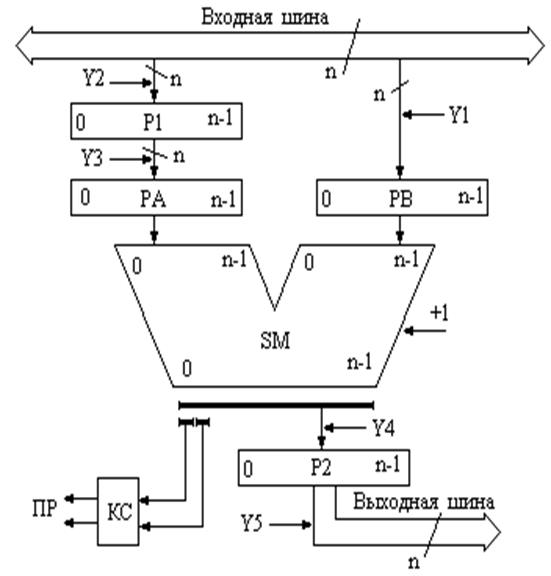

Рассмотрим схему АЛУ для сложения чисел с фиксированной запятой, передаваемых по общей шине. Она приведена на рис. 5.36.

Основой АЛУ является n – разрядный комбинационный сумматор. Операнды поступают по общей входной шине в регистры РА и РВ, которые поочерёдно подключают к шине с помощью тристабильных элементов. Первое слагаемое (уменьшаемое) помещается в регистре РВ. Второе слагаемое (вычитаемое) помещается в регистре Р1, который связан с регистром РА цепями прямой и инверсной передачи кода. Прямая передача используется при сложении, а инверсная при вычитании (выполняется сложение в дополнительном коде). Операция вычитания заменяется сложением: Z = X - Y = X + (-Y), а в младший разряд результата добавляется единица. Результат выдаётся в регистр Р2.

Комбинационная схема (КС) следит за переносами в знаковый разряд и из него и вырабатывает признак результата - ПР (флаг): больше нуля (ПР =01), меньше нуля(ПР =10), равно нулю (ПР = 00), переполнение разрядной сетки (ПР =11).

Рисунок 5.36 – Схема АЛУ для сложения чисел

Составим микропрограмму сложения двух чисел.

Y1: РВ = ![]() слово1

слово1![]()

![]()

![]()

Y2: Р1 = ![]() слово2

слово2![]()

![]()

![]()

Y3: РА = Если сложение то Р1 иначе ![]()

Y4: Р2 = Если сложение то РА + РВ иначе РА+ РВ + 1

Y5: Если ПР = 11 то переполнение иначе ![]() вых. шина

вых. шина ![]() =

Р2

=

Р2

Конец

Для выполнения операций умножения, деления, логических операций схема АЛУ дополняется другими элементами.

6 Запоминающие устройства

6.1 Основные понятия

Память цифровых систем (запоминающие устройства - ЗУ) это совокупность технических средств, предназначенных для приема, хранения и воспроизведения информации, представленной двоичными кодами. Основными характеристиками систем памяти являются:

· Информационная емкость (бит или байт);

· Быстродействие – время от момента обращения к ЗУ до появления требуемой информации на выходе (время доступа) или количество воспроизводимой информации в единицу времени (бит/с);

· Энергопотребление – мощность на единицу информационной емкости (Вт/бит).

По назначению все ЗУ делятся на несколько видов:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.