При обращении к динамическому ОЗУ предполагается дважды выставлять на шине адреса адрес ячейки памяти (адрес строки и адрес столбца). Обычно обращение ведется к данным, лежащим в соседних ячейках памяти, поэтому не обязательно при считывании или записи каждый раз передавать адрес строки.

Такой режим обращения к динамическому ОЗУ называется быстрый страничный режим доступа FPM (Fast Page Mode) что сокращает время доступа к памяти почти в полтора раза. Временная диаграмма режима FPM приведена на рисунке 6.17.

Рисунок 6.17 - Временная диаграмма обращения к динамическому ОЗУ

в режиме FPM

Еще одним способом увеличения быстродействия ОЗУ является применение EDO (Extended Data Out – ОЗУ с расширенным выходом данных). В EDO ОЗУ усилители-регенераторы не сбрасываются по окончанию строба CAS, поэтому считывание данных происходит ещё быстрее.

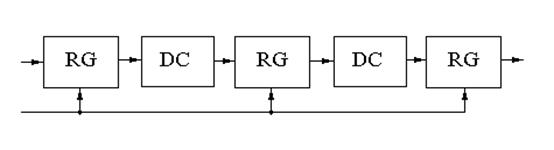

Следующим шагом в развитии схем динамического ОЗУ стало применение в составе ОЗУ счетчика столбцов. То есть при переходе адреса ячейки к следующему столбцу матрицы, адрес столбца инкрементируется автоматически. Такое ОЗУ получило название BEDO (ОЗУ с пакетным доступом). Для уменьшения времени регенерации при считывании одной ячейки памяти в строке запоминающей матрицы регенерируется вся строка. В стробируемом ОЗУ (SDRAM) увеличение быстродействия получается за счет применения конвейерной обработки сигнала. Как известно, при использовании конвейера можно разделить отдельные операции, такие как выборка строк, выборка столбцов, считывание ячеек памяти и производить эти операции одновременно. При этом, пока на выход передаётся считанная ранее информация, производится дешифрация столбца для текущей ячейки памяти и производится дешифрация строки для следующей ячейки памяти. Этот процесс иллюстрируется рисунком 6.18.

Рисунок 6.18 - Структурная схема конвейерной обработки данных

Из этого рисунка видно, что при одиночном обращении к такой схеме ОЗУ время доступа увеличивается, при считывании же нескольких соседних ячеек памяти общее быстродействие динамического ОЗУ возрастает.

6.5 Построение памяти требуемого объёма

Подводя итоги, можно сказать, что, несмотря на большое разнообразие типов микросхем памяти (ПЗУ и ОЗУ), все они имеют сходную структуру: накопитель, дешифратор и схему управления чтением/записью.

При построении систем памяти наибольшее распространение получили БИС ЗУ с конфигурацией М х1бит (М = 256,512,1024,2048,4096 …). Хотя БИС с другой конфигурацией и выпускаются, но они применяются реже.

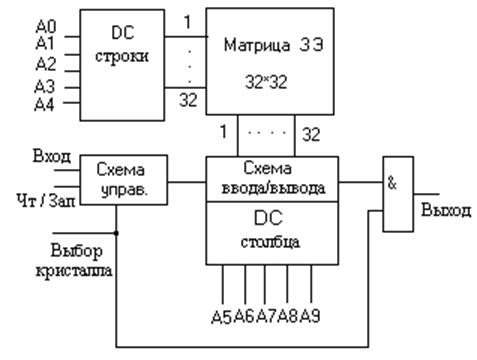

Типовая структура статического МОП ЗУ с организацией 1К х1бит приведена на рисунке 6.19.

Рисунок 6.19 – Типовая структура статического ЗУ с организацией 1К х 1

Основой ЗУ является матрица запоминающих элементов (ЗЭ) размером 32 х 32. Первые пять разрядов адреса указывают номер строки, последние пять - номер столбца. Схема управления переключает режим чтения / записи по внешнему управляющему сигналу. Обращение к данной схеме возможно только при наличии сигнала выбор кристалла (CS = 1). Этот вход нужен для построения блоков памяти большого объема. Особенностью этой системы является независимость входных и выходных данных. Если шина данных двунаправленная, то требуются дополнительные цепи, объединяющие вход и выход. Структурная схема ОЗУ с общими выводами для входных и выходных сигналов приведена на рисунке 6.20.

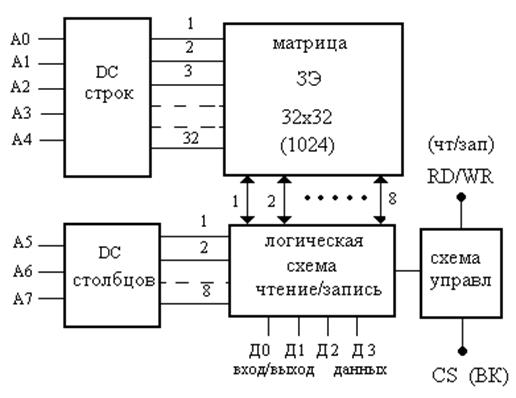

Рисунок 6.20 – Типовая структура статического ЗУ

с организацией 256 х 4 и общей шиной данных

Емкость ЗУ равна 1024 бит, но организация другая - 256 х 4. Для выбора требуемого четырехразрядного слова используется пятиразрядный DC строк и трехразрядной DC столбцов, выбирающий одно из восьми слов в строке.

Память имеет разрядность равную или кратную разрядности данных. Для восьмиразрядного МП нужна память с длиной слова восемь бит.

При объединении нескольких микросхем памяти в общий блок происходит наращивание памяти по “горизонтали” или по “вертикали”.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.