б) Виділити один

або декілька вхідних контактів, вимкнути інструмент Fan-In і натиснути інструмент палітри Displays

the fan-out to the selected item(s) – відображати вихідні зв’язки

виділен(ого/их) елемент(а/ів) – (або в меню Options

вибрати опцію Show Node Fan-Out – показати вихідні зв’язки кіл) і

спостерігати логічні зв’язки у вигляді зелених ліній. Так само виділити одну

або декілька логічних комірок і спостерігати їх зв’язки з виходами;

б) Виділити один

або декілька вхідних контактів, вимкнути інструмент Fan-In і натиснути інструмент палітри Displays

the fan-out to the selected item(s) – відображати вихідні зв’язки

виділен(ого/их) елемент(а/ів) – (або в меню Options

вибрати опцію Show Node Fan-Out – показати вихідні зв’язки кіл) і

спостерігати логічні зв’язки у вигляді зелених ліній. Так само виділити одну

або декілька логічних комірок і спостерігати їх зв’язки з виходами;

в) Виділити одну або декілька логічних комірок, ввімкнути обидва інструменти (Fan-In та Fan-Out) і спостерігати логічні зв’язки комір(ки/ок) зі входами і виходами (як подано на ілюстрації);

г) Виділити дві або декілька логічних комірок (утримувати клавішу Shift), натиснути інструмент палітри Displays the path between selected items – відображати шлях між виділеними елементами – (або в меню Options вибрати опцію Show Path – показати шлях) і спостерігати логічні зв’язки у вигляді синіх ліній.

G Примітка. Команда Show Path дозволяє лише з’ясувати наявність або відсутність зв’язків між виділеними комірками; за її ввімкнення автоматично вимикаються дві інші команди (Fan-In та Fan-Out).

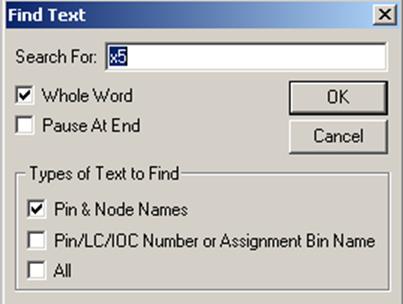

д) Піктограмою панелі інструментів (або з меню

Utilities > Find Text) викликати діалогове

вікно Find Text (знайти текст), у

віконці Search For (пошук) ввести, наприклад, назву входу х5, на вкладці Types of Text to Find вибрати Pin

& Node Names (імена контактів і

кіл) та натиснути ОК. Після цього шуканий контакт буде виділений та частина

плану складної мікросхеми з цим елементом пересунеться в поле зору вікна;

д) Піктограмою панелі інструментів (або з меню

Utilities > Find Text) викликати діалогове

вікно Find Text (знайти текст), у

віконці Search For (пошук) ввести, наприклад, назву входу х5, на вкладці Types of Text to Find вибрати Pin

& Node Names (імена контактів і

кіл) та натиснути ОК. Після цього шуканий контакт буде виділений та частина

плану складної мікросхеми з цим елементом пересунеться в поле зору вікна;

е) Аби з’ясувати зв’язок

елемента на плані мікросхеми з проектними файлами слід виділити, наприклад,

логічну комірку LC1 і натиснути піктограму панелі інструментів

(або меню Utilities > Find

Node in Design File > натиснути ОК у діалоговому віконці Find Node in Design File). Після цього з’явиться проектний файл із зазначеним

елементом, наприклад, схемою суматора;

е) Аби з’ясувати зв’язок

елемента на плані мікросхеми з проектними файлами слід виділити, наприклад,

логічну комірку LC1 і натиснути піктограму панелі інструментів

(або меню Utilities > Find

Node in Design File > натиснути ОК у діалоговому віконці Find Node in Design File). Після цього з’явиться проектний файл із зазначеним

елементом, наприклад, схемою суматора;

G Примітка. Якщо в проектному файлі імена входів або виходів інші, з’явиться повідомлення, що якийсь контакт не знайдено. Деякі компоненти проектного файла можуть бути відсутніми на плані мікросхеми, якщо компілятором було інакше синтезовано проект.

ж) Аби з’ясувати розміщення

елемента проектного файла на плані мікросхеми, слід відкрити цей файл,

наприклад, 500sum.gdf, виділити елемент і

натиснути піктограму панелі інструментів (або меню Utilities > Find Node in Floorplan > натиснути ОК у діалоговому віконці Find Node in Floorplan). Після цього з’явиться план мікросхеми Floorplan з виділеними

комірками або контактами, в яких розміщено заданий елемент.

ж) Аби з’ясувати розміщення

елемента проектного файла на плані мікросхеми, слід відкрити цей файл,

наприклад, 500sum.gdf, виділити елемент і

натиснути піктограму панелі інструментів (або меню Utilities > Find Node in Floorplan > натиснути ОК у діалоговому віконці Find Node in Floorplan). Після цього з’явиться план мікросхеми Floorplan з виділеними

комірками або контактами, в яких розміщено заданий елемент.

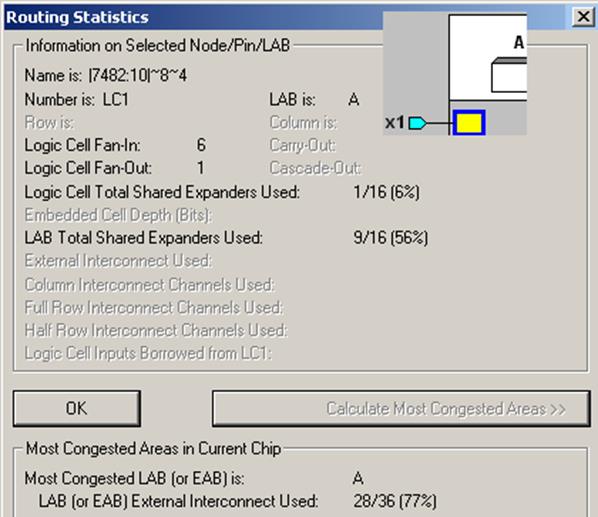

9.2.1.5 Переглянути інформацію про використання ресурсу мікросхеми. Для цього подвійним клацанням на комірці (показано фрагмент на ілюстрації), на контакті або лотоці призначень (або виділити один чи декілька з цих елементів і в меню Options вибрати опцію Routing Statistics – статистика маршрутизації) викликати вікно Routing Statistics з інформацією про використання ресурсу мікросхеми для з’єднання логічних елементів. Відтак натиснути кнопку Calculate Most Congested Areas (обчислити область мікросхеми, в якій залишилось найменше ресурсу) і зчитати інформацію з вікна статистики.

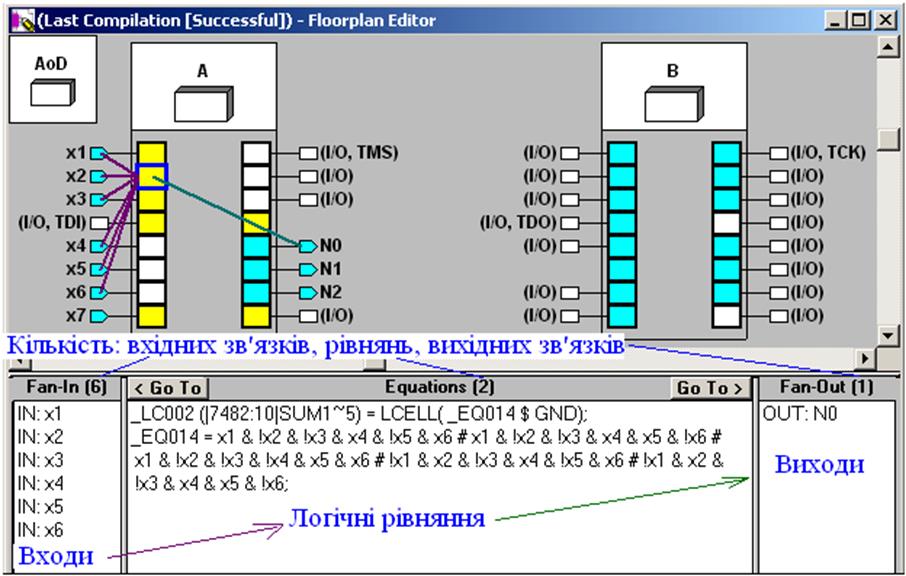

9.2.1.6 Переглянути логічні рівняння і їх

зв’язок з елементами плану мікросхеми:

9.2.1.6 Переглянути логічні рівняння і їх

зв’язок з елементами плану мікросхеми:

а) У меню Layout (розташування) вибрати Report File Equation Viewer (вікно перегляду рівнянь звітного файла) та для зручності встановити в цьому ж меню Full Screen (повний екран). Внизу екрана з’явиться вікно для рівнянь;

б) Клацнути на логічній комірці – у вікні відобразяться сформовані в ній рівняння. Вікно Report File Equation Viewer (див. ілюстрацію вище) складається з трьох частин (ширину кожної з них можна змінити перетягуванням перегородки). Власне рівняння розташовано в центральній частині, у лівій – вхідні сигнали, з яких формуються терми рівнянь, а в правій – вихідні сигнали, для формування яких використовуються рівняння;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.