Контрольні питання та завдання

1. Як слід каскадувати дешифратори з метою збільшення розрядності?

2. Як пов’язані між собою кількість входів і виходів у повних шифраторі та дешифраторі?

3. Запишіть вирази для вихідних логічних функцій 1) шифратора 8 ´ 3, 2) дешифратора 3 ´ 8, 3) стробованого дешифратора 3 ´ 8 та побудуйте їх схеми.

4. Спроектуйте на дешифраторах перетворювач коду, варіант якого задано числом у табл. 3.4, де в лівій колонці наведено вхідний код, а у верхньому рядку – вихідний. Наприклад, варіанту 8 відповідає перетворювач коду 8421 ® 8421доп. У табл. 3.4 подано: ДДК 8421, 8421доп, 8421+3, 2421, 7421, ХҐ – цифри 0...9 чотирирозрядного коду Ґрея, а також коди для відображення на семисегментному індикаторі знаків: Z1 – цифр 0...9, Z2 – літер латиниці A, b, C, d, E, F, H, U, O та Z3 – літер кирилиці А, Г, Е, Н, О, П, Р, С, У.

Таблиця 3.4

|

Коди |

Z1 |

Z2 |

Z3 |

XҐ |

742 |

242 |

8421 + 3 |

8421доп |

|

8421 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

8421доп |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

– |

|

8421+3 |

17 |

18 |

19 |

20 |

21 |

22 |

– |

23 |

|

2421 |

25 |

26 |

27 |

28 |

29 |

– |

30 |

31 |

|

7421 |

33 |

34 |

35 |

36 |

– |

37 |

38 |

39 |

|

XҐ |

41 |

42 |

43 |

– |

44 |

45 |

460 |

47 |

4 МУЛЬТИПЛЕКСОРИ

Мета роботи: дослідження типових мультиплексорів, проектування ЦКП на мультиплексорах; групи і шини; мегафункції, основи їх настроювання, менеджер автоматичного створення мегафункцій, запровадження мегафункцій до графічного і текстового файлів та застосування їх для побудови цифрових пристроїв.

Домашнє завдання

! Спроектувати ЦКП для реалізації логічної функції, заданої згідно з варіантом завдання (див. додаток А, варіанти завдання 4), на мультиплексорах різної розрядності та вибрати оптимальний варіант.

4.1 Стислі теоретичні відомості

4.1.1 Принцип побудови мультиплексорів

Мультиплексором (multiplexеr, MUX) m : 1 (“з m в 1”) називається комутатор сигналів з m каналів в один, а стробований мультиплексор називається також мультиплексором-селектором (multiplexеr-selector, MS).

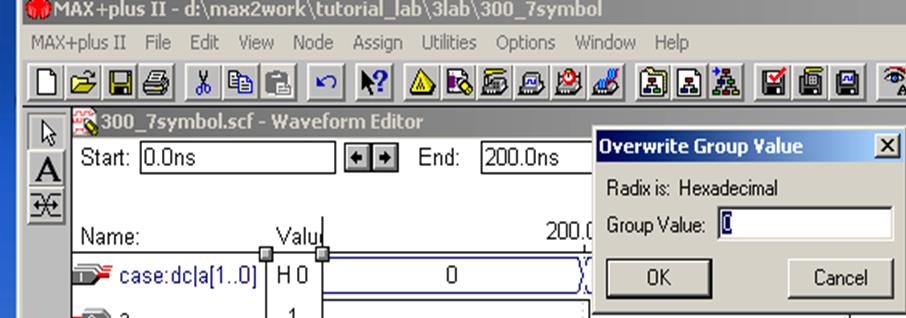

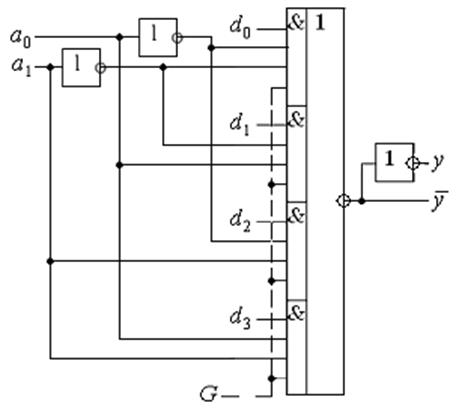

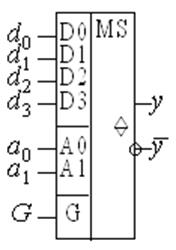

Залежно від адреси А = а1а0 (рис. 4.1,а) до виходу у мультиплексора має надходити один із вхідних сигналів d0 ... d3, тобто

![]() (4.1)

(4.1)

де уi - вихідні функції дешифратора.

а) б) в)

Рисунок 4.1 – Принцип побудови мультиплексора

Схему за виразом (4.1) можна реалізувати на елементі І-АБО-НЕ (рис. 4.1,б): за адресою а1а0 рівень логічної одиниці з’являється на всіх входах тільки одного з елементів І, що дозволяє проходити відповідному вхідному сигналові di до виходу. Стробовий вхід G мультиплексора-селектора (пунктир на рис. 4.1, б) при застосуванні елементів з трьома станами (рис. 4.1, в) розширює функціональні можливості схеми.

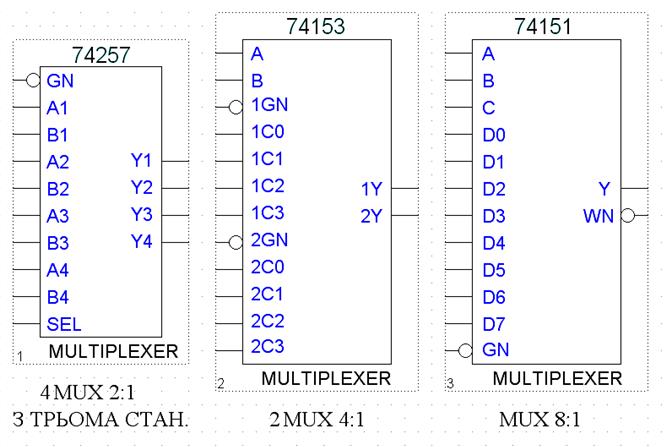

Рисунок 4.2

Таким чином, мультиплексор має k адресних, m = 2k інформаційних входів та один вихід (або два взаємоінверсні виходи). Серед ІС мультиплексорів, що випускаються серійно (рис. 4.2), найпоширенішими є з розрядністю адреси k = 1, 2, 3. Вони забезпечують перемикання m = 2, 4, 8 входів до одного виходу.

Розширення розрядності здійснюють шляхом каскадування

мультиплексорів. З цією метою старший розряд адреси (рис. 4.3) з’єднують зі

стробовим входом одного мультиплексора безпосередньо, а другого – через інвертор

і виходи об’єднують через елемент АБО. Коли зазначений розряд а3

= 0, до виходу комутуються молодші біти d0...d7, а при а3 =

1 – старші d8...d15. Є і інші

способи каскадування.

Розширення розрядності здійснюють шляхом каскадування

мультиплексорів. З цією метою старший розряд адреси (рис. 4.3) з’єднують зі

стробовим входом одного мультиплексора безпосередньо, а другого – через інвертор

і виходи об’єднують через елемент АБО. Коли зазначений розряд а3

= 0, до виходу комутуються молодші біти d0...d7, а при а3 =

1 – старші d8...d15. Є і інші

способи каскадування.

4.1.2 Групи і шини

4.1.2.1 Одновимірні групи

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.