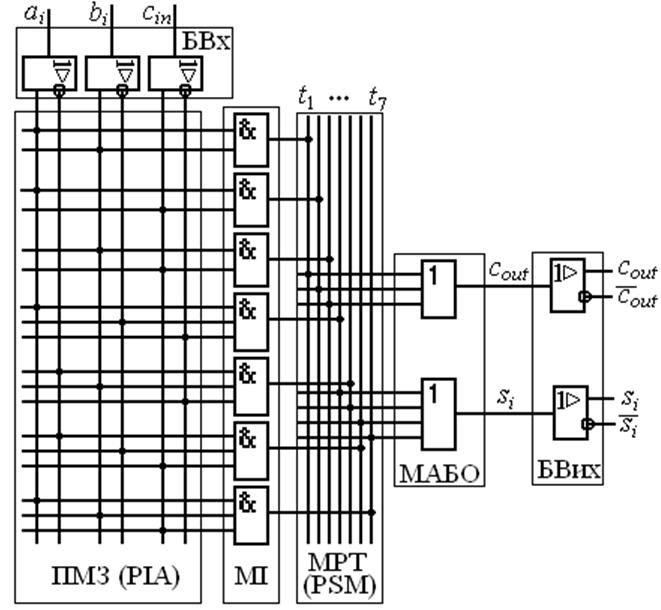

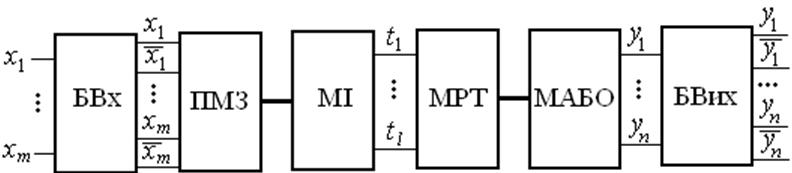

Таким чином, структурна схема ПЛМ набуває вигляду рис. 9.4, б). З числа m змінних х1 ... хm у матриці І формуються терми t1 ... tl, отже, кількість l кон’юнкторів дорівнює числу термів. Відтак у матриці АБО утворюються функції y1...yn, тому кількість диз’юнкторів n дорівнює числу функцій. Розмірність матриці m: l: n є одним з основних її параметрів. Другим важливим параметром є швидкодія, яка для схеми на рис. 9.4, а) буде найбільшою для базових елементів певного типу через двоступеневу (без урахування буферів) реалізацію функцій.

а)

б)

Рисунок 9.4

Проте задля ощадливості щодо ресурсу і гнучкості побудови вдаються до розширення функціональних можливостей ПЛМ. Так, складність схеми (див. рис. 4,а) q = 9 / 25 (кількість логічних елементів без буферів / загальна кількість їх входів) можна зменшити до q = 7 / 14 (рис. 3,в) за спільної схемної мінімізації (див. п. 2.1.3). Перетворенням схеми (див. рис. 9.3, в) до структури І, АБО

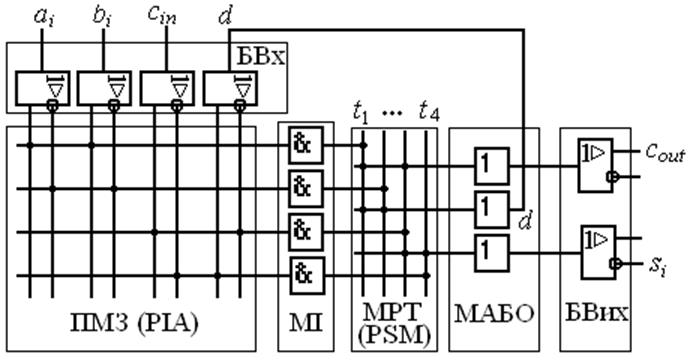

дістанемо реалізацію суматора на ПЛМ (рис. 9.5). На цій схемі подано загальноприйняте для ВІС і НВІС спрощене зображення елементів: багатовходові кон’юнктури і диз’юнктори замінюються одновходовими. Якщо на горизонтальній лінії, що відображає входи елемента, є точка перетину з вертикальною сигнальною лінією, то ця змінна з’єднується зі входом елемента, а якщо точка відсутня, то не з’єднується. Отже, кількість точок на горизонтальній лінії дорівнює числу задіяних входів елемента.

Рисунок 9.5

Спрощення ПЛМ відбувається завдяки так званому розділюваному (спільному) розширенню: спільні вертикальні лінії термів МРТ використовуються неодноразово для утворення диз’юнкцій у МАБО та паралельному розширенню: диз’юнкції з виходу окремих елементів АБО (у прикладі диз’юнкція d) знов повертаються до ПМЗ для утворення інших логічних функцій. Проте через збільшення глибини реалізації збільшується також і затримка поширення сигналів, так само, як і на рис. 9.3, в).

9.1.2 Архітектура ПЛІС

9.1.2.1 План розміщення ПЛІС

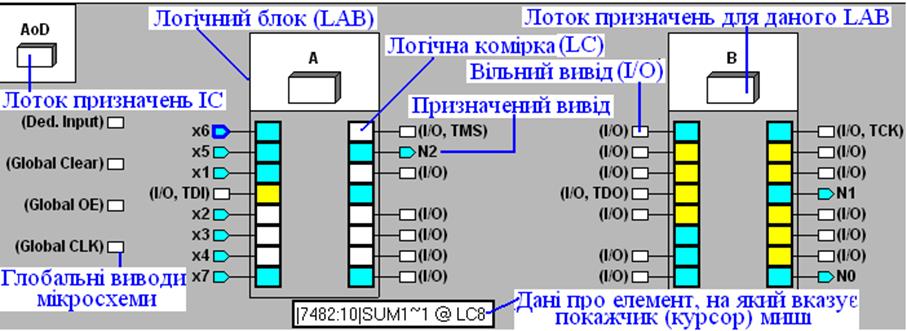

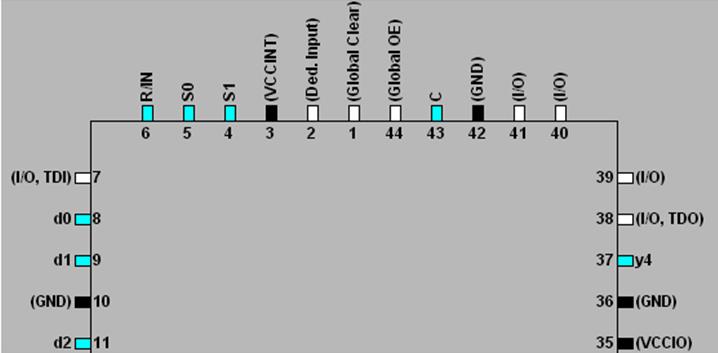

ПЛІС, що крім багатьох ПЛМ містить регістри, буфери, розгалужену систему програмованих з’єднань тощо, структурована на окремі частини. У загальному вигляді ці частини зображаються в САПР на плані її розміщення (Floorplan) як подано на рис. 9.6, а). Компілятор автоматично призначає елементи схеми, необхідні для реалізації проекту, виконує потрібні з’єднання і вносить всю цю інформацію до програмувального файла (після цього проектувальник має змогу скоригувати призначення вручну і знов перекомпілювати проект). Призначення (Assignments) для мікросхеми на плані розміщення містяться в лотку AoD (Anywhere on Device) і відображаються при натисканні на нього.

Найбільшою функціональною частиною ПЛІС є логічний блок ЛБ (Logic Array Block, LAB), в якому згруповано набір логічних ресурсів таким чином, що будь-який сигнал є доступний для кожного елемента набору. На плані ЛБ позначено літерами А, В біля лотків, в яких відображаються призначення відповідного блоку. ПЛІС однієї родини однотипні і відрізняються кількістю ЛБ; у прикладі подано ІС родини МАХ3000А найменшої складності з двох ЛБ, а ІС цієї родини найбільшої (на цей час) складності містить 32 такі блоки.

а)

б)

Рисунок 9.6

Наступною за ієрархією складовою частиною є логічна комірка ЛК (Logic Cell, LCELL, LC), яка в технічній документації для ПЛІС з електричним стиранням (EЕPROM-based) називається макрокоміркою МК (Macrocell, MC). Кожний ЛБ розглядуваного типу ПЛІС містить 16 макрокомірок, а їх загальна кількість у мікросхемі визначає її назву. Так, у родині МАХ3000А найпростіша мікросхема МАХ3032А містить у двох логічних блоках 32 макрокомірки, а найскладніша МАХ3512А – 512 МК у складі 32 ЛБ. Призначені (задіяні) комірки на плані забарвлюються, а вільні залишаються білими.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.