У D-тригері з прямим синхровходом

на елементах І-НЕ (див. рис. 6.5, а) пасивним рівнем С =

0 вхідні елементи І-НЕ блокують проходження інформації до комірки пам’яті:

незалежно від значення D на обох входах ![]() асинхронного

асинхронного

![]() -тригера встановлюються рівні логічної

1 і підтримують його в режимі схову, а з надходженням активного рівня C =

1 вхідні елементи виконують функції інверторів інформаційного сигналу і тригер

функціонує за перемикальною таблицею (рис. 6.4, б). За допомогою

додаткових входів (пунктир на рис. 6.5, а) утворюється тригер зі входом

дозволу Е, який схемно є паралельним входові С і відрізняється

від нього лише призначенням: за постійного рівня Е = 0 тригер

блокується, а при Е = 1 функціонує як звичайний D-тригер.

-тригера встановлюються рівні логічної

1 і підтримують його в режимі схову, а з надходженням активного рівня C =

1 вхідні елементи виконують функції інверторів інформаційного сигналу і тригер

функціонує за перемикальною таблицею (рис. 6.4, б). За допомогою

додаткових входів (пунктир на рис. 6.5, а) утворюється тригер зі входом

дозволу Е, який схемно є паралельним входові С і відрізняється

від нього лише призначенням: за постійного рівня Е = 0 тригер

блокується, а при Е = 1 функціонує як звичайний D-тригер.

Внаслідок додаткової затримки сигналів у вхідних елементах І-НЕ, як зазначено позиціями кодів на схемі рис. 6.5, а) та кількістю затримок tз.п на часових діаграмах рис. 6.5, в), тривалість перемикання синхронного тригера збільшується на одну затримку порівняно з асинхронним і становить tT = 3tз.п, тривалість синхроімпульсів для надійного перемикання має бути не меншою за ti ³ 3tз.п, а тому роздільна здатність тригера, тобто період синхроімпульсів Т ³ 4tз.п і робоча частота f £ 1/4 tз.п.

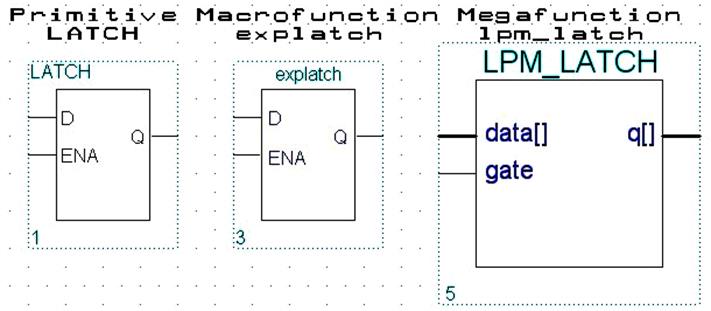

6.1.3.3 Примітив, макро- і мегафункція D-тригерів. Слід звернути увагу на те, що, як зазначено на часових діаграмах, перемикання відбуваються з надходженням імпульсів С, відносно них і відлічуються затримки в елементах. Крім того, протягом C = 1 інформаційний сигнал D має бути незмінним, інакше пристрій функціонуватиме як асинхронний. З огляду на це асинхронні тригери (див. рис. 6.3) і синхронні зі статичним керуванням (рис. 6.6) позначаються в програмному забезпеченні терміном Latch („замок”), а їх синхровхід – терміном ENA (Enable – дозвіл) або gate (ворота).

Рисунок 6.6

6.1.3.4RSC-тригери. Синхронні RS-тригери з прямими (RSC тригер) та інверсними (![]() -тригер) входами є тригерами з двофазним

записом інформації (рис. 6.7, а), б). При С = 0 тригер типу RSC

(див. рис. 6.7, а) перебуває в режимі схову незалежно від

значення інформаційних сигналів R, S (рис. 6.7, в), а при С

= 1 він функціонує за правилами асинхронного тригера (див. рис. 6.1, д).

Так само

-тригер) входами є тригерами з двофазним

записом інформації (рис. 6.7, а), б). При С = 0 тригер типу RSC

(див. рис. 6.7, а) перебуває в режимі схову незалежно від

значення інформаційних сигналів R, S (рис. 6.7, в), а при С

= 1 він функціонує за правилами асинхронного тригера (див. рис. 6.1, д).

Так само ![]() -тригер (див. рис. 6.7, б)

пасивним рівнем

-тригер (див. рис. 6.7, б)

пасивним рівнем ![]() = 1 підтримується в

початковому стані (рис. 6.7, г), а з надходженням активного рівня

= 1 підтримується в

початковому стані (рис. 6.7, г), а з надходженням активного рівня ![]() = 0 функціонує як асинхронний

= 0 функціонує як асинхронний ![]() -тригер (див. рис. 6.1, е).

-тригер (див. рис. 6.1, е).

За діаграмою термів RSC-тригера (рис. 6.7, д), складеною, як і раніше, з урахуванням попереднього стану Q, мінімізуємо характеристичне рівняння

Q+ = СS + ![]() Q, якщо СRS =

0, (6.5)

Q, якщо СRS =

0, (6.5)

з обмежувальною умовою, що виключає заборонену комбінацію вхідних сигналів СRS = 1. З рівняння виходить, що при С = 0 у тригері забезпечується режим схову Q+ = Q, а при С = 1 вираз (6.5) перетворюється до (6.1).

|

а) |

в) |

г) |

д) |

|

б) |

|||

|

е) |

ж) |

и) |

|

Рисунок 6.7

Таблиця переходів і граф RSC-тригера (рис. 6.7, е), ж) відрізняються лише доповненням стійких станів при С = 0 та сигналу C = 1 при інших переходах. Часто користуються вкороченою таблицею переходів, яка вказує переходи Q ® Q+ тільки при C=1; тоді вона збігається з таблицею RS‑тригера (див. рис. 6.1, и) і функції збудження при C = 1 збігаються з (6.2).

За допомогою паралельних входів кінцевого асинхронного тригера (див. рис. 6.1, в), 6.2, а) синхронні тригери різних типів можуть виконуватися з одним, наприклад, R¢або двома R¢ /, S¢ / установлювальними входами (рис. 6.7, и), призначеними для асинхронного (незалежно від рівнів усіх інших сигналів) установлення до визначеного стану, найчастіше для скидання до Q = 0 перед виконанням певної операції. Синхронні тригери типів RC, SC, ЕС при C= 0 зберігають початковий стан, а при C= 1 функціонують за правилами відповідних асинхронних тригерів (п. 6.1.2.2).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.