Отже, час

затримки поширення сигналу від входів до виходів тригера, тобто тривалість його

перемикання до повного усталення вихідного коду при переході від стану 0 до

стану 1 та навпаки, становить t01 = t10 = tT

= 2tз.п. Тригер надійно спрацює, тобто не зможе

повернутися до попереднього стану за зникнення активного рівня вхідного

сигналу, якщо цей сигнал триватиме до закінчення процесу регенеративного

перемикання: ti ³ 2tз.п. Проте,

якщо активний сигнал на другому вході з’явиться одразу ж після перемикання

тригера, тривалість одного з вихідних сигналів (на виході ![]() діаграми) буде меншою за 2tз.п,

що недостатньо для надійного спрацьовування аналогічного навантажувального

каскаду. Через це роздільний час тригера – мінімальний інтервал між

надходженням вхідних імпульсів – має становити T ³ 3tз.п,

а робоча частота чергування імпульсів f £ 1/3tз.п.

діаграми) буде меншою за 2tз.п,

що недостатньо для надійного спрацьовування аналогічного навантажувального

каскаду. Через це роздільний час тригера – мінімальний інтервал між

надходженням вхідних імпульсів – має становити T ³ 3tз.п,

а робоча частота чергування імпульсів f £ 1/3tз.п.

Для RS-тригера на елементах

АБО-НЕ (див. рис. 6.2, б) згідно з аксіомою х + 0 = х

пасивними є рівні логічного 0 і він функціонує за таблицею на рис. 6.1, д). Швидкодія

RS-тригера, як видно з позицій станів на схемі та часових діаграм (рис. 6.2, г),

визначається так само, як для ![]() тригера.

тригера.

|

а) |

б) |

|

в) |

г) |

|

Рисунок 6.2 |

|

Тригери ![]() та

RS можна перетворити один до одного за допомогою інверторів на їх входах.

Кілька інших різновидів асинхронних тригерів відрізняються від RS-тригера переходом

під час дії забороненої для нього комбінації відповідно до станів: тригера типу

S – до Q+ = 1, типу R – до Q+ = 0 та типу Е (Exclusive – винятковий, особливий) – перебуванням у режимі схову Q+ = Q.

та

RS можна перетворити один до одного за допомогою інверторів на їх входах.

Кілька інших різновидів асинхронних тригерів відрізняються від RS-тригера переходом

під час дії забороненої для нього комбінації відповідно до станів: тригера типу

S – до Q+ = 1, типу R – до Q+ = 0 та типу Е (Exclusive – винятковий, особливий) – перебуванням у режимі схову Q+ = Q.

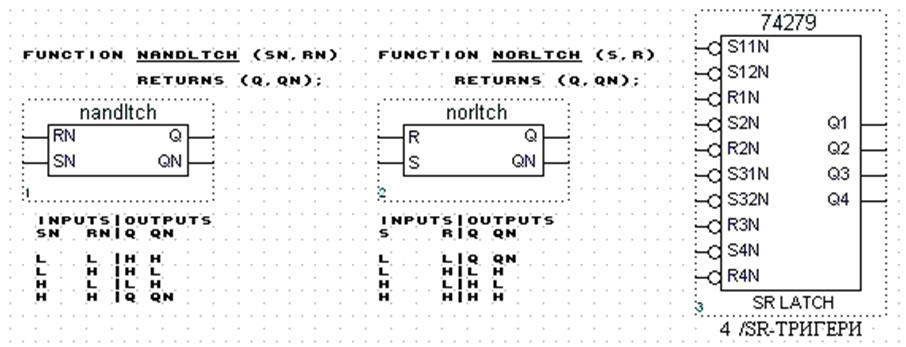

6.1.2.3 Макрофункції. Специфічні для програми макрофункції асинхронних RS-тригерів (елементи з позиційними номерами 1, 2 на рис. 6.3) і ІС жорсткої структури серії 74 (елемент 3) цілком відповідають тригерам з інверсними і прямими входами в базисах І-НЕ та АБО-НЕ (див. рис. 6.2, а), б).

Рисунок 6.3

6.1.3 Синхронні тригери зі статичним керуванням

6.1.3.1D-тригери. Ознакою синхронних тригерів є наявність входу синхронізації С (Сlock). D-тригерами називаються синхронні тригери з однофазним записом інформації (Data – дані) за входом D. Інформація до D-три-гера надходить одним дротом (рис. 6.4, а), що зручно для міжкаскадного сполучення, тому D-тригери набули поширення в інтегральній схемотехніці.

|

а) |

б) |

в) |

г) |

Рисунок 6.4

За відсутності синхроімпульсу (С = 0) тригер перебуває в режимі схову Q+ = Q (рис. 6.4, б), а під час дії активної частини синхроімпульсу (С = 1) до нього записується біт інформації Q+ = D. Характеристичне рівняння, отримане з діаграми термів (рис. 6.4, в)

Q+ = СD + ![]() Q, (6.3)

Q, (6.3)

як і перемикальна таблиця, свідчить, що режим схову забезпечується тільки

завдяки синхровходові, отже, асинхронний D-тригер не має сенсу: при С =

1 за виходом Q він еквівалентний повторювачу, а за виходом ![]() – інвертору. Не має сенсу також тригер

з інверсним входом D – досить взаємно замінити позначення виходів Q

та

– інвертору. Не має сенсу також тригер

з інверсним входом D – досить взаємно замінити позначення виходів Q

та ![]() для перетворення тригерів з прямим і

інверсним входом D.

для перетворення тригерів з прямим і

інверсним входом D.

Згідно з (6.3) при С = 1 та довільному вихідному стані функція збудження набуває вигляду:

D = Q+, якщо С = 1, Q = Х. (6.4)

Для зручності керування застосовуються тригери різного типу з додатковим входом Е (Enable – дозвіл). Так, DE-тригер (рис. 6.4, г) при Е = 0 перебуває в початковому стані незалежно від інших сигналів, а при Е = 1 перемикається як звичайний D-тригер.

|

а) |

в) |

|

б) |

|

|

Рисунок 6.5 |

|

6.1.3.2 Схемна реалізація D-тригерів. Для

схемної реалізації синхронних тригерів зі статичним керуванням (рис. 6.5, а), б)

за допомогою додаткових логічних елементів з вхідних інформаційних сигналів

формують на входах комірки пам’яті (асинхронного RS-тригера) активні рівні сигналів

![]() або R0, S0

в інтервалах часу, що задаються рівнем синхроімпульсів С,

або R0, S0

в інтервалах часу, що задаються рівнем синхроімпульсів С, ![]() , а в проміжках між синхроімпульсами

ці рівні мають бути пасивними.

, а в проміжках між синхроімпульсами

ці рівні мають бути пасивними.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.