Процедуру фізичного програмування однієї мікросхеми в системі з інтерфейсними завантажувальними пристроями BitBlaster, ByteBlasterMV або MasterBlaster, а також типи ІС (із підтримуваних даною версією пакету MAX+PLUS II), які можна програмувати в такий спосіб, наведено в розділі довідкиProgramming a Single Device with the BitBlaster, ByteBlasterMV, or MasterBlaster;

б) Програмування ланцюжка мікросхем. Стандарт IEEE Std 1149.1 інтерфейсу JTAG дозволяє поширити схему периферійного сканування BST на низку мікросхем, якщо послідовно ввімкнути їх тестові входи TDI і виходи ТDO даних (рис. 9.14, б). Таке ввімкнення, що утворює ланцюжок JTAG (JTAG chain), застосовується для створення пристроїв та систем з кількох мікросхем. Схема з’єднань для програмування ланцюжка JTAG не відрізняється від схеми програмування однієї ІС (див. рис. 9.14, а).

Процедуру фізичного програмування ланцюжка мікросхем з інтерфейсними завантажувальними пристроями BitBlaster, ByteBlasterMV або MasterBlaster, а також типи ІС (із підтримуваних даною версією пакету MAX+PLUS II), які можна програмувати в такий спосіб, наведено в розділі довідкиProgramming Multiple Devices in a JTAG Chain with the BitBlaster, ByteBlasterMV, or MasterBlaster;

в) Конфігурування мікросхем. Схеми конфігурування однієї ІС в системі і кількох ІС ланцюжка JTAG аналогічні схемам програмування (див. рис. 9.13), відрізняються лише назви і кількість виводів ІС для конфігурування, з’єднаних на платі зі стандартним рознімачем.

Процедуру конфігурування однієї ІС і ланцюжка мікросхем з інтерфейсними завантажувальними пристроями, а також типи ІС (із підтримуваних даною версією пакету MAX+PLUS II), які можна конфігурувати в такий спосіб, наведено в розділах довідки відповідноConfiguring a Single Device with the BitBlaster, ByteBlasterMV, MasterBlaster, or FLEX Download Cable та Configuring Multiple Devices in a JTAG Chain with the BitBlaster, ByteBlasterMV, or MasterBlaster;

г) Програмування

мікросхеми апаратним програматором. Мікросхему, зокрема, якщо її виконано

без інтерфейсу JTAG, можна запрограмувати в окремому вигляді,

використовуючи апаратний засібпрограмування, а після того

встановити на робочу плату пристрою або системи. У такий спосіб програмування

здійснюється базовим модулем програматора Master

Programming Unit (MPU) або Altera Programming Unit (АPU – для Windows 98 та Windows

2000). Базовий модуль з’єднується з комп’ютером за допомогою плати

програматора, а мікросхема з’єднується зMPU через програмувальний

адаптер, завдяки чому забезпечується доступ до всіх зовнішніх виводів ІС. Тип

адаптера вибирається залежно від родини ІС, типу її корпуса і кількості

штирків, про що можна дізнатися з довідки Help

> Devices & Adapters

> Adapters.

г) Програмування

мікросхеми апаратним програматором. Мікросхему, зокрема, якщо її виконано

без інтерфейсу JTAG, можна запрограмувати в окремому вигляді,

використовуючи апаратний засібпрограмування, а після того

встановити на робочу плату пристрою або системи. У такий спосіб програмування

здійснюється базовим модулем програматора Master

Programming Unit (MPU) або Altera Programming Unit (АPU – для Windows 98 та Windows

2000). Базовий модуль з’єднується з комп’ютером за допомогою плати

програматора, а мікросхема з’єднується зMPU через програмувальний

адаптер, завдяки чому забезпечується доступ до всіх зовнішніх виводів ІС. Тип

адаптера вибирається залежно від родини ІС, типу її корпуса і кількості

штирків, про що можна дізнатися з довідки Help

> Devices & Adapters

> Adapters.

9.2 Лабораторне завдання

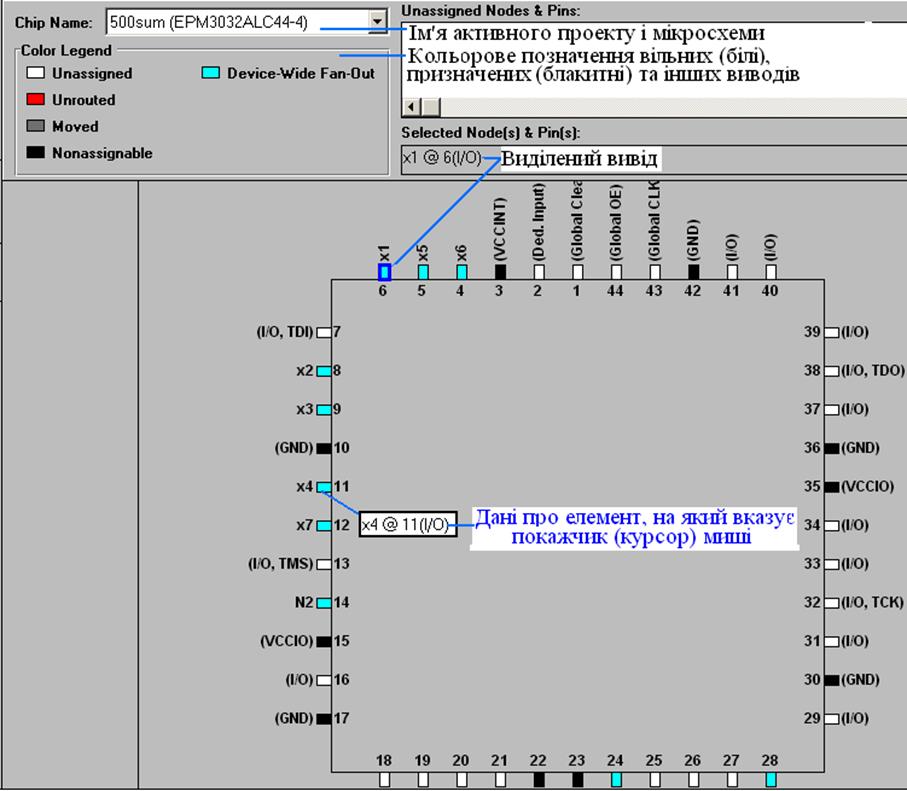

9.2.1 Засвоїти основи використання редактора фізичного розміщення Floorplan Editor

9.2.1.1

Активізувати потрібний проект, наприклад, 5lab\5XXsum (ввести до рядка заголовку Manager його назву),

піктограмою (або з меню MAX+plus II > Floorplan Editor) викликати редактор розміщення Floorplan Editor

та переглянути результати реалізації проекту компілятором:

9.2.1.1

Активізувати потрібний проект, наприклад, 5lab\5XXsum (ввести до рядка заголовку Manager його назву),

піктограмою (або з меню MAX+plus II > Floorplan Editor) викликати редактор розміщення Floorplan Editor

та переглянути результати реалізації проекту компілятором:

а)

У разі потреби подвійним клацанням в робочому полі вікна Floorplan Editor або з меню Layout (розташування)

> Device View (вигляд мікросхеми)

викликати вікно Device View із загальним виглядом мікросхеми. Відтак

натиснути на вертикальній палітрі інструмент відображення інформації про

останню компіляцію (або в меню Layout виставити прапорець Last Compilation Floorplan) та ознайомитися з призначеною

компілятором мікросхемою.

а)

У разі потреби подвійним клацанням в робочому полі вікна Floorplan Editor або з меню Layout (розташування)

> Device View (вигляд мікросхеми)

викликати вікно Device View із загальним виглядом мікросхеми. Відтак

натиснути на вертикальній палітрі інструмент відображення інформації про

останню компіляцію (або в меню Layout виставити прапорець Last Compilation Floorplan) та ознайомитися з призначеною

компілятором мікросхемою.

б) Подвійним клацанням всередині мікросхеми або з меню Layout (розташування) > LAB View (вигляд логічних блоків) викликати вікно з виглядом внутрішньої структури, в якому ознайомитися з логічними блоками (LAB) і їх комірками (LC), призначеними компілятором.

9.2.1.2 Відредагувати розміщення вхідних і вихідних контактів ІС з метою зручного їх розташування на друкованій платі та перекомпілювати проект:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.