Таблиця 8.1

Таблиця 8.1

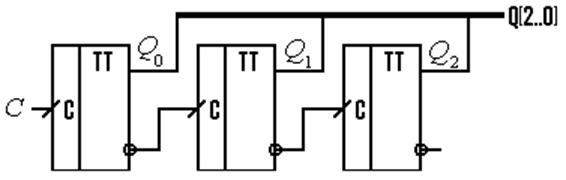

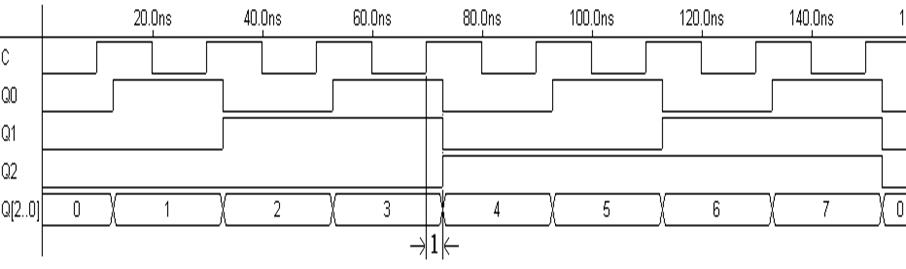

Отже, лічильник можна побудувати послідовним

увімкненням ланцюжка Т-тригерів. З огляду на те, що негативному перепаду

напруги на прямому виході тригера відповідає позитивний перепад на його

інверсному виході, при використанні Т-тригерів з прямим динамічним керуванням

необхідно з’єднувати їх синхровходи з інверсними виходами попередніх розрядів ![]() (рис. 8.1, а). І, навпаки,

синхровходи Т-тригерів з інверсним динамічним керуванням слід з’єднувати з

прямими виходами попередніх розрядів Сі = Qі-1.

(рис. 8.1, а). І, навпаки,

синхровходи Т-тригерів з інверсним динамічним керуванням слід з’єднувати з

прямими виходами попередніх розрядів Сі = Qі-1.

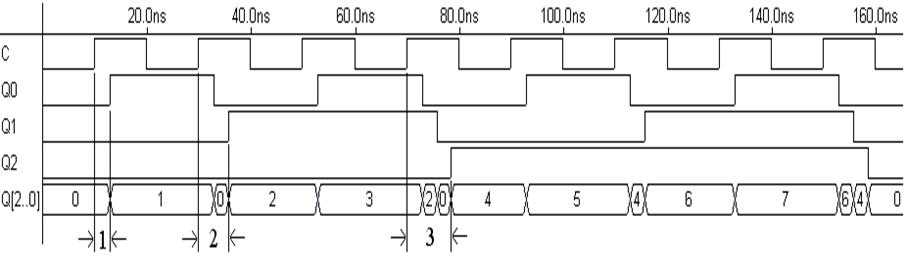

У таких лічильниках з послідовним перенесенням (послідовних лічильниках) кожний наступний тригер перемикається із запізненням відносно фронту вихідного сигналу попереднього розряду, а тригер молодшого розряду – відносно лічильних імпульсів С на час перемикання тригера tT. Через це час усталення вихідного коду лічильника, який визначається за перемикання всіх розрядів, залежить від їх кількості і становить tл=ntT (на рис. 1,б кількість затримок tT позначено цифрами). З огляду на відсутність спільного для всіх розрядів синхровходу і внаслідок цього неодночасність їх перемикання послідовні лічильники є асинхронними.

а)

б)

Рисунок 8.1

Перевагою лічильників з послідовним перенесенням є їхня простота через регулярність структури і мінімум міжз’єднань, що сприяє також підвищенню завадостійкості, а недоліком – низька швидкодія та залежність її від розрядності n: зі збільшенням модуля лічби M зростає і час усталення tл. Крім того, під час перемикання виникають хибні стани, наприклад, перехід вихідного коду від 3 до 4 супроводжується проміжними станами 2 і 0 (див. рис. 8.1, б), що може бути небезпечним для роботи пристроїв, сполучених з виходами лічильника. Отже, вихідний код зчитують після закінчення перехідного процесу його усталення, тобто через час tл.

Проте у вимірювальній техніці, коли з метою підвищення вірогідності результатів підраховують пачки імпульсів і зчитування коду виконують після закінчення низки таких пачок, ці недоліки не є суттєвими. Не впливають вони також на поділ частоти: як видно з діаграм на рис. 8.1, б), частота сигналу на виході кожного наступного розряду зменшується вдвічі. Для подібних застосувань максимальна частота вхідного сигналу обмежується лише часом перемикання тригера молодшого розряду fмакс = 1/tT (бо кожний наступний розряд перемикається з удвічі меншою частотою, ніж попередній), тобто в цьому разі послідовні лічильники мають найвищу швидкодію і потребують мінімум ресурсу мікросхем.

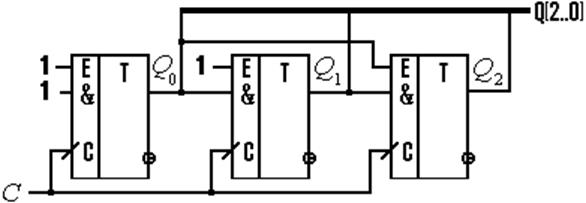

8.1.2.2 Лічильники з паралельним перенесенням. Як видно з перемикальної таблиці двійкового лічильника (див. табл. 8.1), кожний наступний його розряд має перемикатися до протилежного стану з надходженням чергового лічильного імпульсу лише за умови перебування всіх попередніх розрядів у стані логічної 1. Так, розряд з виходом Q1 перемикається зі станів N = 1, 3, 5, 7, коли Q0 = 1, а з виходом Q2 – зі станів N = 3, 7, коли Q0 = Q1 = 1. Отже, синхровходи тригерів всіх розряди можна з’єднати паралельно з лічильним входом, якщо дозвіл на перемикання і-го розряду здобути шляхом логічного множення сигналів з виходів усіх попередніх розрядів Ei = Q0Q1 … Qi-1 і побудувати лічильник на ТЕ-тригерах (рис. 8.2, а).

а)

б)

Рисунок 8.2

У таких лічильниках з паралельним перенесенням (паралельних лічильниках) усі розряди, на входах дозволу яких діють рівні логічної 1, перемикаються одночасно (рис. 8.2, б), тому час усталення вихідного коду визначається затримкою перемикання лише одного тригераі становить tл = tT. З огляду на те, що синхровхід для всіх розрядів є спільним і внаслідок цього вони перемикаються одночасно, паралельні лічильники є синхронними.

ТЕ-тригери

з кількома входами дозволу Е утворюються на основі JK-тригерів шляхом

об’єднання паралельних входів J та K, а за браком таких паралельних входів – за допомогою

додаткових елементів І. Проте базовою є схема паралельного лічильника на

економічних D-тригерах,

яку можна синтезувати з урахуванням функції збудження D-тригера ![]() .

Безпосередньо з перемикальної таблиці (див. табл. 8.1) вносимо до діаграм

термів значення Qi+ (рис. 8.3, а) і мінімізуємо функції збудження

лічильника:

.

Безпосередньо з перемикальної таблиці (див. табл. 8.1) вносимо до діаграм

термів значення Qi+ (рис. 8.3, а) і мінімізуємо функції збудження

лічильника:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.