3.1.2 Дешифратори

Дешифратором (DС – decoder) називається перетворювач m-розряд-ного двійкового коду до n-розрядного унітарного; при цьому розрядність коду розширюється, бо n > m. Дешифратори найчастіше застосовуються для вибору (селекції) інтегрованої мікросхеми або іншого пристрою з метою обміну інформацією, наприклад, для адресування до окремих комірок пам’яті.

За допомогою вхідного m-розрядного коду дешифратор спроможний керувати n = 2m вихідними лініями, що є розрядами унітарного коду. Такий дешифратор є повним, а якщо n < 2m – неповним. Наприклад, дешифратори 1:2, 2:4, перетворювачі двійкового коду в унітарні вісімковий 3:8 і шістнадцятковий 4:16 є повними, а перетворювач тетради ДДК до унітарного десяткового коду 4:10 є неповним.

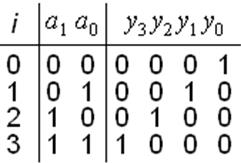

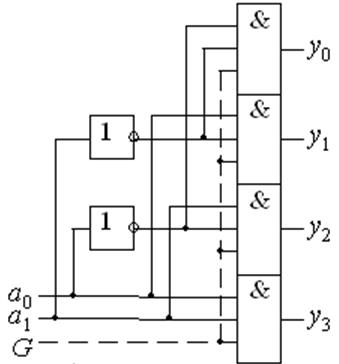

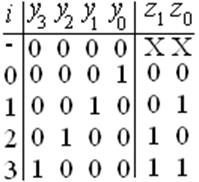

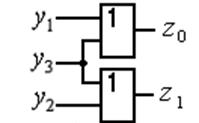

Принцип побудови дешифратора розглянемо на прикладі перетворення двійкового коду А=а1а0 в унітарний Y=у3у2у1у0 (рис. 3.2, а). З огляду на те, що кожна з вихідних функцій визначається одним мінтермом, вона вже є мінімальною:

![]() (3.1)

(3.1)

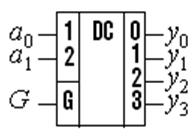

Взагалі, при m змінних функції повного дешифратора реалізуються за допомогою n = 2m елементів І з m входами кожний (рис. 3.2, б). Активний рівень з’являється тільки на тому виході дешифратора, номер якого відповідає вхідному кодові. Наприклад, при а1а0 = 102 = 210 дві одиниці прикладено до входів тільки одного елемента І з виходом у2, тому у2 = 1, а на всіх інших виходах встановлюються рівні логічного 0. Визначити номер активного виходу дуже просто: досить скласти ваги розрядів на вхідному полі умовного графічного позначення дешифратора (рис. 3.2, в), на яких діють рівні логічної 1.

а) б) в)

Рисунок 3.2 – Принцип побудови дешифратора

Якщо додаткові входи елементів І з’єднати зі спільним входом G(від Gate – ворота) як на рис. 3.2, б) позначено пунктиром, здобудемо стробований дешифратор (див. рис. 3.2, в). При G= 0 елементи І блоковано і на всіх прямих виходах встановлюються рівні логічного 0, а при G= 1 схема функціонує як звичайний дешифратор. За допомогою входів Gможна синхронізувати роботу дешифраторів, а також виконувати їх каскадування.

3.1.3 Демультиплексори

Демультиплексором 1 : n (“з 1 в n”) називається комутатор сигналів з одного в n каналів. На відміну від механічного перемикача комутування таким пристроєм здійснюється за допомогою цифрових кодів. Функцію демультиплексора виконує дешифратор зі стробовим входом G(див. рис. 3.2, б), в), якщо вхід G використовувати як інформаційний х: адресним, наприклад, дворозрядним кодом А = а1а0 активізується тільки один елемент I, тому на виході уi цього елемента з’являється сигнал х. З огляду на це стробований дешифратор називають також дешифратором-демуль-типлексором. Отже, демультиплексор має один інформаційний, k адресних входів та n = 2k виходів; при k = 2, 3, 4 кількість виходів становить відповідно n = 4, 8, 16.

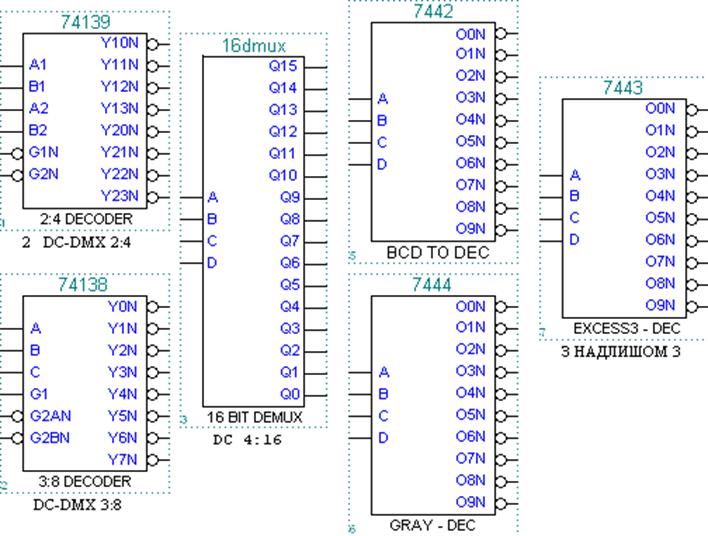

Крім повних дешифраторів серії 74 (рис. 3.3), у тому числі стробованих 2:4, 3:8 та спеціалізованої макрофункції дешифратора 4:16, у бібліотеці є також стандартні неповні дешифратори 4:10 кодів ДДК, Ґрея і ДДК з надлишком три.

3.1.4 Шифратори

Шифратор (СD – Encoder) є перетворювач m-розрядного унітарного коду до n-розрядного двійкового коду. Шифратор m : n здійснює стискання інформації, бо n < m. Типовим його застосуванням є зв’язок між блоками, зокрема, уведення інформації з клавіатури: при натисненні однієї з клавіш на виході шифратора утворюється тетрада ДДК десяткової цифри або двійковий комбінаторний код літери чи іншого символу.

Рисунок 3.3 – Спеціалізовані макрофункції дешифраторів

Вихідний n-розрядний код шифратора спроможний відобразити інформацію, що надходить до нього по m = 2n лініях, тобто 2n розрядів унітарного коду. Такий шифратор є повним, а якщо m < 2n – неповним. Наприклад, повними є шифратори 4:2, 8:3, а перетворювач унітарного десяткового коду в тетради ДДК 10:4 є неповним.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.