· Линейный код на интерфейсе S/T.

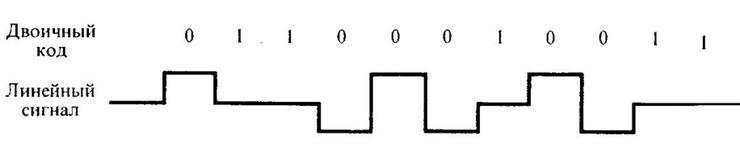

Передача данных ведется квазитроичным кодом AMI (Alternate Mark Inversion) – рис.7.44.

“0”, сформированный в двоичном коде, в AMI представляется с помощью импульса напряжениемприблизительно 750 мВ положительной или отрицательной полярности. Паузой в коде AMI представляется “1”. Если последовательно передается два “0”, то в линейном коде формируется биполярное нарушение.

Рис.7.44 Передача данных кодом AMI

· Доступ оконечных терминалов к D -каналу.

Любой вызов со стороны оконечного терминала TE начинается с сигнализации по D -каналу. Для того, чтобы в случае шинной конфигурации «точка – многоточие» оконечные терминалы не мешали друг другу при одновременной передаче сигналов в D -канал, должна выполняться определенная процедура доступа к этому каналу. В каждый момент времени по конкретному В-каналу передает и принимает информацию только один оконечный терминал.

Механизм доступа к D -каналу основан на использовании принципа ЭХО D -канала. Эхо информацией D -канала являются биты Е. Любой сигнальный бит, переданный от TE по D -каналу в NT, транслируется обратно в ТЕ в виде битов Е. Если D -канал свободен, то по нему непрерывно передается логическая "1". ТЕ воспринимает D -канал как свободный, если он получает по ЭХО D -каналу (биты Е) заданное число X следующих друг за другом "1". Для каждого ТЕ число последовательно поступающих "1" определяется исходя из протокола канала D и в соответствии с приоритетом самого ТЕ. В соответствии с протоколом канала в рабочем (занятом) его состоянии может передаваться последовательно максимально 6 логических "1", которые входят в состав флага структуры блока сигнальной информации. Аварийный сигнал передается по D-каналу семью последовательными единицами. Из вышесказанного ясно, что самый приоритетный TE должен иметь значение X = 8.

Если канал свободен, то ТЕ немедленно начинает сигнализацию по D -каналу. В дальнейшем ТЕ следит за ЭХО D –каналом, т.е. за битами Е. Принятые значения битов Е оконечный терминал ТЕ сравнивает с переданными значениями соответствующих битов по D -каналу. Отсутствие полного совпадения, возможно, означает возникновение конфликтной ситуации – другой TE также пытается занять канал. Поэтому ТЕ прекращает передачу сигнальной информации и пытается вновь занять D -канал. После успешной передачи информации по D -каналу ТЕ снижает свой приоритет, увеличивая значение X на единицу и давая возможность другим ТЕ занять D -канал. Длительность ожидания занятия канала D зависит от приоритета информации, которую нужно передать и от того, была ли уже у данного TE перед этим успешная попытка передачи. Сигнальная информация обладает высшим приоритетом, а низкоскоростная пользовательская пакетная информация – низшим приоритетом. Внутри каждой группы информации с одинаковым приоритетом более низким приоритетом обладают те TE, которые недавно уже осуществили успешную передачу по D-каналу. Таким образом выравниваются возможности всех TE, включенных в NT по установлению соединений.

· Структура цикла.

Все сигналы управления и информационные сигналы передаются в обоих направлениях с использованием временного разделения в рамка цикла (250 мкс), содержащего 48 бит. В течение 1с передается 4000 циклов. Это соответствует скорости группового цифрового потока 192 кбит/с (48 x 4000). На рис.7.45 приведена структура цифрового потока S/T интерфейса, а также возможные квазитроичные уровни сигнала для каждого бита.

Рис.7.45 Структура цикла на интерфейсе S/T

В течение одного цикла осуществляется передача 16 бит каждого В -канала и 4 бита D -канала. Схема чередования битов В- и D-каналов в одном цикле на S/T интерфейсе следующая:

Канал: В1 D В2 D В1 D В2 D

Число битов: 8 1 8 1 8 1 8 1

Как указывалось выше, BRI содержит два В -канала и один D -канал (2В+D). Однако возможно компоновать BRI как 1В+D или как 0В+D, т.е. D. Тогда временные отрезки для передачи битов В-канала остаются незанятыми и заполняются логическими "1".

Момент начала цикла, передаваемого от ТЕ к NT всегда смещен на два бита относительно начала цикла от NT к ТЕ. Таким образом, NT управляет синхронизацией всех ТЕ. Структуры циклов передаваемых от TE к NT и в обратном направлении в основном одинаковые, за исключением того, что структура цикла от NT к ТЕ содержит ЭХО биты D -канала (Е -биты).

Назначение Е –битов было описано выше.

Бит F в начале каждого цикла необходим для цикловой синхронизации и является признаком начала цикла. F -бит всегда имеет положительную полярность. Организация цикловой синхронизации основана на искусственном нарушении чередования полярностей кода AMI.

L -бит используется, для выравнивания постоянных составляющих тока при передаче данных. Полярность бита L всегда противоположна полярности бита цикловой синхронизации.

В Рекомендациях I.430 ITU -T определяется возможность образования сверхцикла из 20 циклов по 250 мкс с помощью соответствующих сигналов, передаваемых во временных интервалах М и Fа. Кроме того Fа -биты используются для дополнительного контроля за цикловой синхронизацией. В направлении передачи от NT к ТЕ вместе с Fа используется N –бит, который всегда устанавливается в инверсное положение по отношению к Fа (т.е., если Fа =1, то N =0 и наоборот).

А -бит, используется при процедуре активизации. С помощью бита A производится управление со стороны узла коммутации процессом включения питания TE при поступлении вызова и выключения питания после окончания обмена информацией.

S -бит зарезервирован для возможного в будущем расширения функций BRI (в настоящее время равны 0).

Таким образом из 48 бит цикла 12 бит – служебные. Поэтому скорость потока данных пользователя BRI составляет 144 кбит/с (36 бит x 4000 циклов).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.