4. Створити проект 10ХХPODIL_ FLEX лабораторного макета для експериментального дослідження ЦПП на мікросхемі FLEX10К на прикладі заданого варіанта подільника частоти за п. 1.1. (див. як зразок файл 1000PODIL_FLEX.bdf – рис. А.9 у додатках).

4.1 Вставити до графічного файлу 10ХХPODIL_ FLEX.bdf копію лабораторногомакета 10ХХPODIL_МАX.bdf, вилучити світлодіоди, скоригувати імена вхідних портів sw[] (якщо якійсь вивід відокремлено від групи, його слід іменувати без квадратних дужок, наприклад, замість sw[8] позначити sw8), відповідно до цих портів скоригувати також трасувальні таблиці блоку подільника частоти та ввести до складу проекту всі потрібні файли. Розвести виводи мікросхеми на друкованій платі відповідно до файлу ../10lab/ROZWED_FLEX.bdf або імпортувати їх призначення з файлу ../10lab/FLEX_pin.bdf і скоригувати відповідно до портів проекту.

4.2 Виконати компіляцію і функціональне моделювання.

4.3 Створити програмувальний CDF-файл і виконати програмування мікросхеми. Виконати фізичне конфігурування мікросхеми (джампери встановити згідно з файлом ../10lab/ FLEX_pin.bdf).

4.4 Розробити методику та виконати експериментальні дослідження пристрою. Порівняти результати експериментальних досліджень з даними проектних файлів, зробити висновки.

Приклад: подільник частоти із коефіцієнтом поділу М = 11 – файли 1000PODIL_FLEX.bdf, vwf.

5. Переглянути особливості фізичного розміщення мікросхеми на плані Floorplan Editor.

5.1

Аналогічно п. 3.1 ознайомитися із цоколівкою виводів, користуючись

інструментами регулювання масштабу.

5.1

Аналогічно п. 3.1 ознайомитися із цоколівкою виводів, користуючись

інструментами регулювання масштабу.

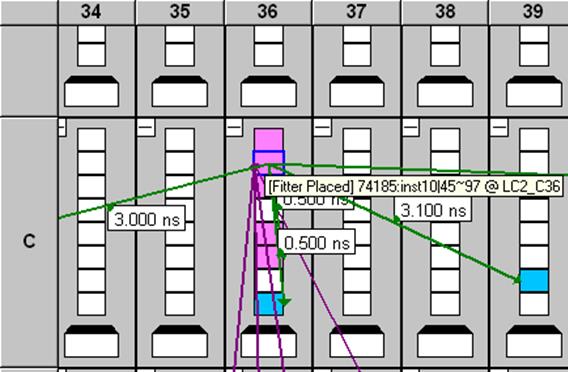

5.2 Аналогічно п. 3.2 ознайомитися з виглядом внутрішньої структури ПЛІС (на фрагменті подано затримки зв’язків комірки LC2 логічного блоку C36).

СЛОВНИК НАЙБІЛЬШ УЖИВАНИХ ТЕРМІНІВ

Булеві рівняння – Boolean Equation.

Властивості виводів – Pin Properties.

Градація швидкодії – Speed grade.

Заголовок –Title Statement.

Застереження – Warning.

Інструментальні засоби ─ Primitive Tools.

Категорії – Categories.

Кількість виводів – Pin count.

Коефіцієнт множення (помножити на…) – Multiplied by.

Комбінаційний вузол – Combinatorial Node.

Компіляція – Compilation.

Логічна секція – Logic Section.

Мова програмування високого рівня – Hardware Description Language.

Настроїти – Customize.

Оголошення вузла – Node Declaration.

Оголошення модуля – Instance Declaration.

Оператор вибору – Case Statement.

Оператор включення – Include Statement.

Оператор прототипу функцій – Function Prototype Statement.

Оператор таблиці відповідності – Truth Table Statement.

Повідомлення – Report.

Повноциклова САПР ─ Electronic design automation.

Показ типів інструментів – Show tooltips.

Порти – Ports.

Призначення – Assignment.

Причина – Cause.

Процесор повідомлень – Message Processor.

Поточне резюме – Flow Summary.

Рівень – Value.

САПР – Computer aided design.

Секція змінних – Variable Section.

Секція підпроекту – Subdesign Section.

Секція підпроекту –Subdesign Section.

Система на програмовному кристалі – System-on-a-programmable-chip.

Система числення – Radix.

Корпус – Package.

Умовний оператор – If Then Statement.

Настроювання апаратного засобу – Hardware Setup.

Файл опису схеми програмування – Chain Description File.

Файл часових діаграм – Vector Waveform File.

Часовий аналіз – Timing Analyse.

Шаблон – Template.

ЛІТЕРАТУРА

1. Кофанов В. Л. Математичні та схемотехнічні основи цифрових пристроїв: Навч. посібник. – Вінниця: УНІВЕРСУМ-Вінниця, 2005. ‑ 165 с.

2. Кофанов В. Л., Осадчук О. В., Гаврілов Д. В.. Лабораторний практикум з дослідження цифрових пристроїв на основі САПР MAX+PLUS II: Навч. посібник. – Вінниця: УНІВЕРСУМ-Вінниця, 2007. ‑ 196 с.

3. Справочник по цифровой схемотехнике / В. И. Зубчук, В. П. Сигорский, А. Н. Шкуро – К.: Техніка, 1990. – 448 с.

4. Угрюмов Е. П. Цифровая схемотехника: Учеб. пособие. – СПб.: БХВ – Петербург, 2002. – 528 с.

5. Кофанов В. Л. Базовые элементы цифровых интегральных микросхем: Учеб. пособие. – К.: УМК ВО, 1988. – 116 с.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.