3.1

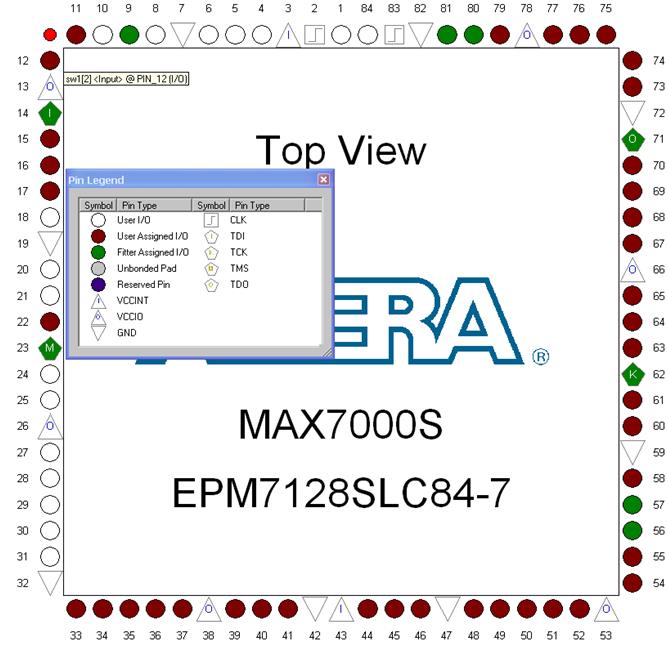

У разі потреби, активізувати належний проект 10XXPODIL_MAX(ввести

його назву до рядка заголовка головного вікна), піктограмою горизонтальної панелі Pin Planner (або з меню Assignments > Pin Planner) відкрити вікно із цоколівкою виводів і розгорнути

його, закривши вікна зі списками. Настроїти

інструментальну палітру (меню Tools > Customize Pin Planner):

встановити великі облямовані кнопки та вилучити зайві інструменти, зокрема, які

є на горизонтальній панелі. Натиснути інструмент вертикальної палітри Pin Legend та ознайомитися з позначенням виводів і розташуванням

їх на цоколівці мікросхеми. Аби з’ясувати призначення виводу, досить підвести

до нього покажчик і зчитати дані в рамці, що з’являється. З меню View

> All Pins List

відкрити вікно зі списком виводів, виділити вивід на цоколівці та зчитати дані

в цьому вікні чи, навпаки, виділити вивід у вікні і продивитися його

розташування на цоколівці. Так само з меню View > Groups List відкрити вікно зі списком груп і аналогічним чином

з’ясувати зв'язок між списком і цоколівкою.

3.1

У разі потреби, активізувати належний проект 10XXPODIL_MAX(ввести

його назву до рядка заголовка головного вікна), піктограмою горизонтальної панелі Pin Planner (або з меню Assignments > Pin Planner) відкрити вікно із цоколівкою виводів і розгорнути

його, закривши вікна зі списками. Настроїти

інструментальну палітру (меню Tools > Customize Pin Planner):

встановити великі облямовані кнопки та вилучити зайві інструменти, зокрема, які

є на горизонтальній панелі. Натиснути інструмент вертикальної палітри Pin Legend та ознайомитися з позначенням виводів і розташуванням

їх на цоколівці мікросхеми. Аби з’ясувати призначення виводу, досить підвести

до нього покажчик і зчитати дані в рамці, що з’являється. З меню View

> All Pins List

відкрити вікно зі списком виводів, виділити вивід на цоколівці та зчитати дані

в цьому вікні чи, навпаки, виділити вивід у вікні і продивитися його

розташування на цоколівці. Так само з меню View > Groups List відкрити вікно зі списком груп і аналогічним чином

з’ясувати зв'язок між списком і цоколівкою.

FПримітки:

1. У зазначеному вікні All Pins можна також відредагувати призначення виводів: клацнути будь-де в рядку потрібного виводу правою кнопкою миші і вибрати в контекстному меню Node Properties для зміни номера виводу або Pin Properties для зміни імені виводу. Відтак в однойменному діалоговому вікні (Node Properties або Pin Properties) в графі Location або Node name прокруткою встановити або надрукувати відповідно номер виводу чи його ім’я. Призначити або відредагувати номер виводу можна і безпосередньо подвійним клацанням у стовпці Location і прокруткою списку номерів. Так само можна відредагувати призначення виводів і у вікні Groups.

2. У зазначених діалогових вікнах (Node Properties або Pin Properties) у графі I/O standard прокруткою можна вибрати також стандарт входу/виходу. За замовчуванням (default) для сімей MAX7000S та FLEX10K встановлено ТТL I/O standard – звичайний стандарт ТТЛ з напругою живлення 5 В (зокрема, через це зазначені сім’ї є популярні серед масових користувачів). Проте для всіх сімей ІС, що підтримуються пакетом Quartus II, можуть використовуватися також низьковольтні (LV) стандарти напруги 3,3 В стосовно вхідних/вихідних сигналів (VCCIO) і напруги 3,3 В/2,5 В стосовно вхідних/вихідних буферів. Такі стандарти для елементної бази ТТЛ (TTL) і КМОНТЛ (CMOS) позначаються в САПР відповідно LVTTL I/O standard та LVCMOS I/O standard.

|

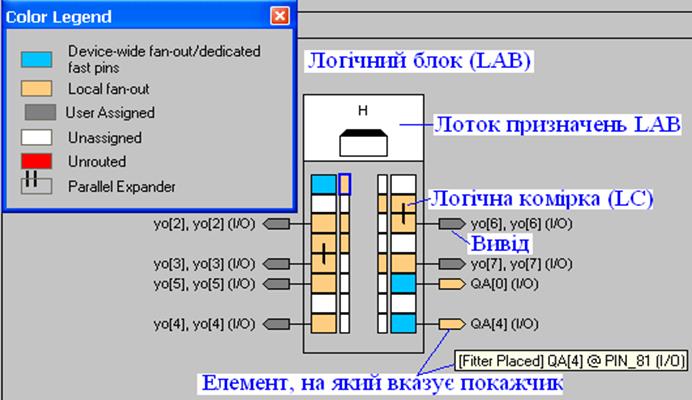

3.2 Піктограмою Timing Closure Floorplan (або з меню Assignments > Timing

Closure Floorplan) відкрити вікно редактора фізичного розміщення Floorplan Editor і розгорнути його. Настроїти інструментальну палітру (меню Tools > Customize

Timing Closure Floorplan): встановити великі облямовані кнопки та вилучити зайві інструменти, зокрема, які є на горизонтальній панелі. Натиснути інструменти вертикальної палітри Show User Assignment (показ призначень користувача), Show Fitter Placements (показ розміщень трасувальника) і View Color Legend (перегляд кольорових позначень) та ознайомитися з виглядом

внутрішньої структури ПЛІС, логічними блоками (LAB), їх комірками (LC) і умовними

позначеннями елементів.

3.2 Піктограмою Timing Closure Floorplan (або з меню Assignments > Timing

Closure Floorplan) відкрити вікно редактора фізичного розміщення Floorplan Editor і розгорнути його. Настроїти інструментальну палітру (меню Tools > Customize

Timing Closure Floorplan): встановити великі облямовані кнопки та вилучити зайві інструменти, зокрема, які є на горизонтальній панелі. Натиснути інструменти вертикальної палітри Show User Assignment (показ призначень користувача), Show Fitter Placements (показ розміщень трасувальника) і View Color Legend (перегляд кольорових позначень) та ознайомитися з виглядом

внутрішньої структури ПЛІС, логічними блоками (LAB), їх комірками (LC) і умовними

позначеннями елементів.

FПримітки:

1. Для перегляду

логічних зв’язків між елементами (між логічними комірками або комірками і

зовнішніми виводами) слід виділити один або декілька елементів (клацнути при

утримуваній клавіші Ctrl), натиснути інструмент палітри Show Node Fan-In (показати вхідні зв’язки кіл) або Show Node Fan-Out (показати вихідні зв’язки кіл) і

спостерігати логічні зв’язки у вигляді кольорових ліній.

1. Для перегляду

логічних зв’язків між елементами (між логічними комірками або комірками і

зовнішніми виводами) слід виділити один або декілька елементів (клацнути при

утримуваній клавіші Ctrl), натиснути інструмент палітри Show Node Fan-In (показати вхідні зв’язки кіл) або Show Node Fan-Out (показати вихідні зв’язки кіл) і

спостерігати логічні зв’язки у вигляді кольорових ліній.

2. Для перегляду

кількості з’єднань між виділеними елементами або затримок між ними слід

натиснути інструмент Show Connection Count або Show Routing Delays.

2. Для перегляду

кількості з’єднань між виділеними елементами або затримок між ними слід

натиснути інструмент Show Connection Count або Show Routing Delays.

3. Для

перегляду логічних рівнянь і їх зв’язок з виділеними елементами плану

мікросхеми слід натиснути інструмент View Equations.

3. Для

перегляду логічних рівнянь і їх зв’язок з виділеними елементами плану

мікросхеми слід натиснути інструмент View Equations.

4. На плані мікросхеми можна також відредагувати розміщення виводів і інших призначень, після чого перекомпілювати проект.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.