З метою збільшення розрядності вдаються до каскадування ІС. Так, з’єднанням трьох стандартних ІС утворюється перетворювач 8 розрядів двійкового коду в ДДК (на рис. 3.1,б наведено його символ, на принципову схему можна вийти з файлу 3libr.bdf), а для перетворення 16-розрядного двійкового коду в ДДК потрібно вже 16 таких ІС.

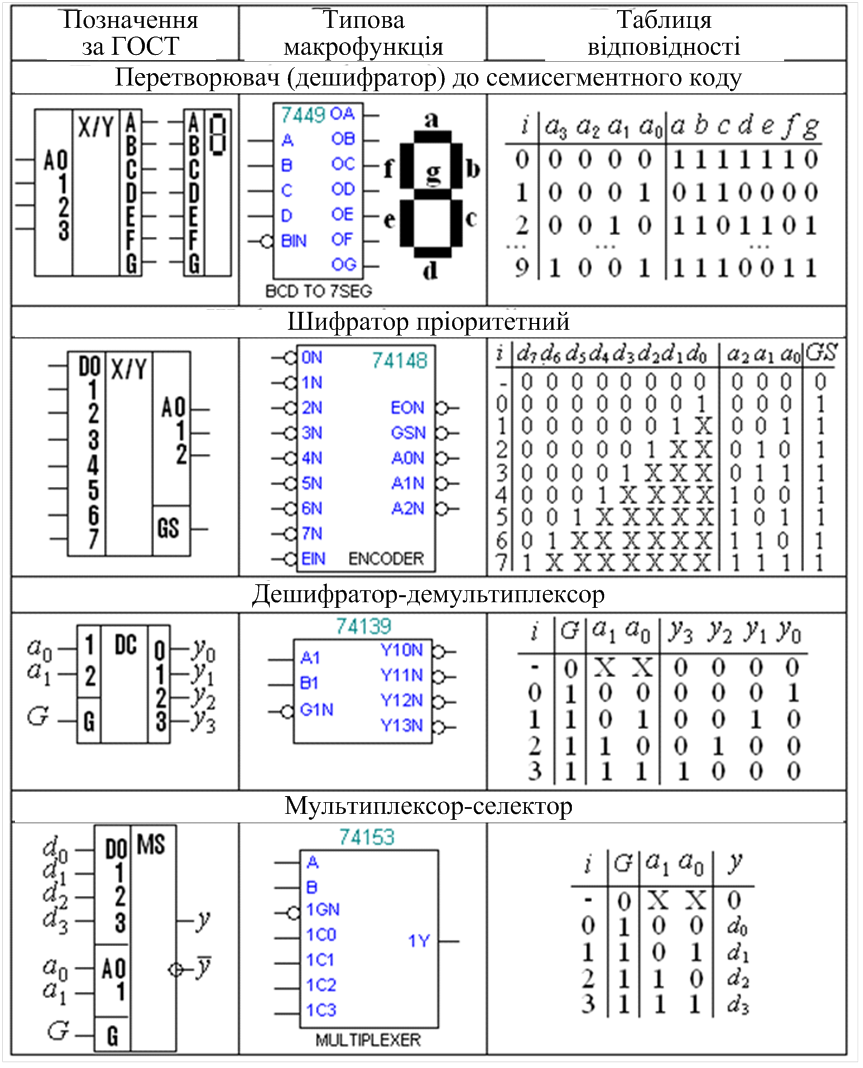

Таблиця 3.1 – Основні ЦКП

Рисунок 3.1 – Типові ІС

Обернене перетворення від ДДК до двійкового коду здійснюється аналогічно. У типовій ІСперетворювача ДДК у двійковий код (рис. 3.1,в) із двох тетрад ДДК (молодшої тетради х3 ... х0 і неповної старшої х5х4) на виходах утворюється семирозрядний двійковий код. Два старші розряди на виходах обох ІС використовуються для перетворення до доповняльних кодів (приклад подано у файлі 3libr.bdf). Докладніше схеми перетворювачів до доповняльних кодів і каскадування різної розрядності наводяться в нормативних документах і довідковій літературі на ІС.

Проектування ЦКП на дешифраторах

Вихідні функції повного дешифратора являють собою набір усіх можливих мінтермів, тому поєднанням виходів дешифратора можна реалізувати будь-яку логічну функцію від його вхідних змінних. На ПЛІС такий прийом використовувати доцільно, якщо він спрощує проектування, а на ІС жорсткої структури застосовувати дешифратори для реалізації простих функцій немає сенсу, крім випадку, коли один з них залишається в корпусі ІС невикористаним. Застосовування дешифраторів може виявитися доцільним для побудови ЦКП з кількома виходами, якщо функція по кожному з них зображається відносно простим поєднанням вихідних функцій дешифратора. При цьому оптимальність рішення з’ясовується шляхом порівняння варіантів схеми на дешифраторах різної розрядності.

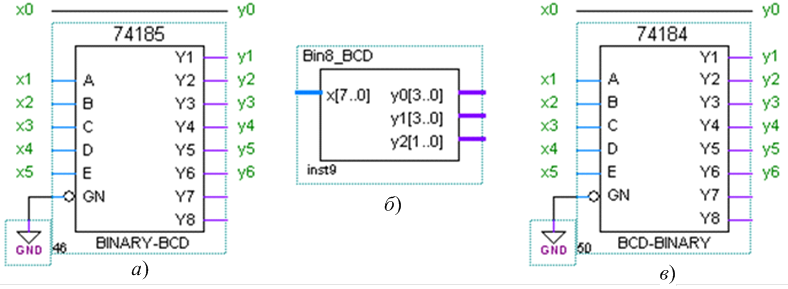

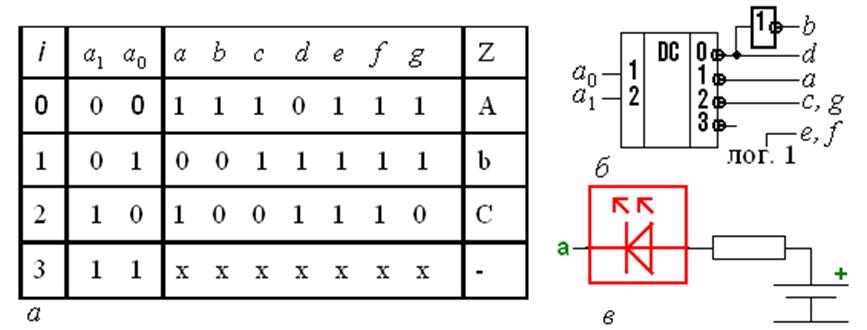

Приклад. Методику проектування ЦКП на основі дешифратора розглянемо на прикладі побудови перетворювача коду для відображення трьох знаків (Z) латиниці. За кількістю потрібних адрес визначаємо розрядність стандартного дешифратора 2:4 і складаємо таблицю відповідності (рис. 3.2,а), в якій зайва адреса і = 3 відповідає факультативним значенням вихідних функцій перетворювача a…g. Відтак виражаємо ці функції через вихідні функції дешифратора:

![]()

і згідно з виразами ![]() будуємо

схему (рис. 3.2,б).

будуємо

схему (рис. 3.2,б).

Якщо сегменти 7-сегментного індикатора

ввімкнено за схемою зі спільним анодом (на рис. 3.2,в зображено еквівалентну схему,

наприклад, сегмента а), вони засвічуватимуться рівнем логічного 0, тому

вихідні функції перетворювача a…gмають бути інверсними відносно

наведених у таблиці на рис. 3.2,а, тобто ![]()

Перевагою використання дешифратора з кількістю адресних входів, що дорівнює кількості змінних m, є відносна простота вихідних функцій, а недоліком – складність такого дешифратора і, головним чином, обмеженість кількості входів, адже при m > 3...4 вже необхідне каскадування дешифраторів на ІС жорсткої структури. З огляду на це може виявитися доцільним варіант побудови схеми на дешифраторі меншої розрядності.

Рисунок 3.2 – Проектування ЦКП на дешифраторі

КОНТРОЛЬНІ ЗАПИТАННЯ

1. Як слід каскадувати дешифратори з метою збільшення розрядності?

2. Як зв’язані між собою кількість входів і виходів у повних шифраторі та дешифраторі?

3. Запишіть вирази для вихідних логічних функцій 1) шифратора 8´3; 2) дешифратора 3´8; 3) стробувального дешифратора 3´8 та побудуйте їх схеми.

4. Спроектуйте на дешифраторах перетворювач коду, варіант якого задано числом у табл. 3.2, де в лівій колонці наведено вхідний код, а у верхньому рядку – вихідний. Наприклад, варіанту 8 відповідає перетворювач коду 8421 ® 8421доп. У табл. 2 подано: ДДК 8421, 8421доп, 8421+3, 2421, 7421, ХГ – цифри 0...9 чотирирозрядного коду Грея, а також коди для відображення на семисегментному індикаторі знаків: Z1 – цифр 0...9, Z2 – літер латиниці A, b, C, d, E, F, H, U, O та Z3 – літер кирилиці А, Г, Е, Н, О, П, Р, С, У.

Таблиця 3.2

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.