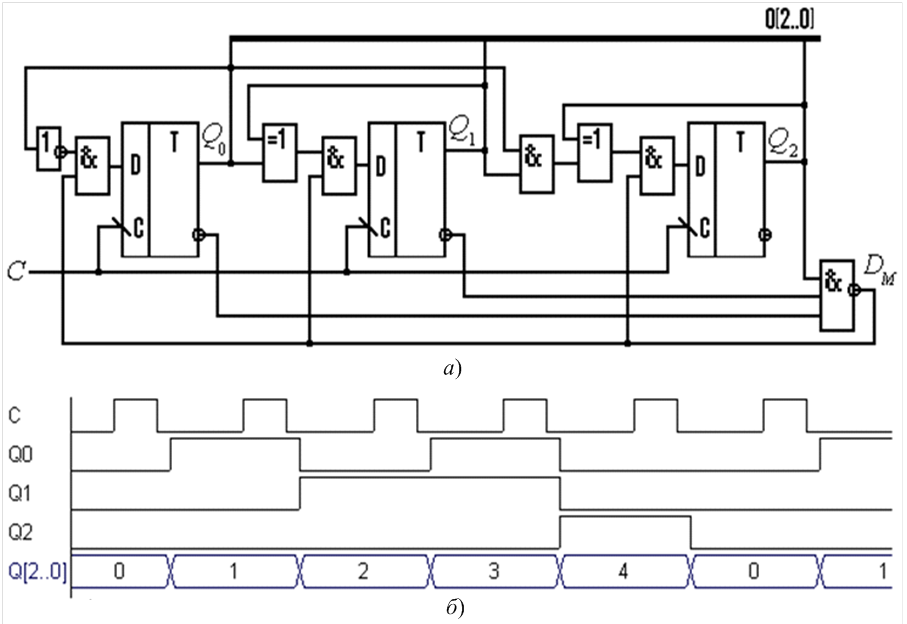

З цією метою на входах Dі тригерів (рис. 9.3,а) увімкнемо додаткові елементи І та за допомогою елемента

І-НЕ сформуємо керувальний сигнал DM. Під час лічби залишається рівень DM = 1, який не впливає на функції

збудження тригерів, а коли вихідний код набуває значення М – 1, цей

рівень змінюється на DM = 0, тому з надходженням чергового імпульсу лічильник

скидається до нульового стану. Для програмування на потрібний модуль лічби

достатньо з’єднати зі входами елемента І-НЕ виходи розрядів відповідно до коду М

– 1. Так, лічильник з модулем М = 5 отримаємо реалізацією числа М – 1 = 410 =

1002 = ![]() (див. рис. 9.3,а). Паралельний лічильник з

довільним модулем такого типу перемикається, як і двійковий, без проміжних

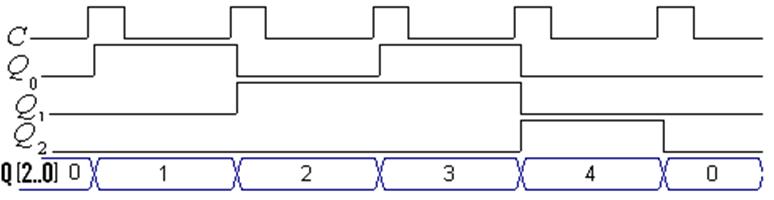

станів під час зміни вихідного коду (рис. 9.3,б).

(див. рис. 9.3,а). Паралельний лічильник з

довільним модулем такого типу перемикається, як і двійковий, без проміжних

станів під час зміни вихідного коду (рис. 9.3,б).

Перевагою лічильників з керованим скиданням є природний порядок лічби, тобто їх можна використовувати за прямим призначенням – для підраховування кількості імпульсів. Проте коли порядок лічби не має значення, наприклад, у подільниках частоти, застосовують також способи перетворення двійкових лічильників у недвійкові шляхом усунення проміжних або молодших станів. В останньому випадку після досягнення максимального коду (всі розряди в одиничному стані) здійснюють примусове нараховування коду на кількість надлишкових станів зі входів передустановлення лічильника. Це спрощує дешифрування за ознакою негативного перепаду на виході старшого розряду.

Рисунок 9.3 – Перетворення двійкового лічильника за основною схемою на D-тригерах у лічильник з програмовним модулем лічби М=2...8

Лічильники зі зворотними зв’язками

Двійкові лічильники утворюються за допомогою прямих міжрозрядних зв’язків – з виходів попередніх на входи наступних розрядів. Запровадженням зворотних зв’язків – з виходів наступних розрядів на входи попередніх – можна шляхом блокування перенесень усунути будь-які надлишкові стани, отже, дістати лічильники з довільним модулем і порядком лічби. Якщо будувати в такий спосіб лічильники з послідовним або комбінованим переносом між окремими розрядами, потрібно визначати функції збудження як інформаційних, так і синхровходів тригерів, а в паралельних лічильників синхровхід всіх розрядів є спільний, тому достатньо знайти функції збудження лише інформаційних входів.

Методику проектування розглянемо на прикладі побудови паралельного лічильника з модулем М = 5 і природним порядком лічби, який має перемикатися за часовими діаграмами на рис. 9.4.

Рисунок 9.4 – Часові діаграми паралельного лічильника з модулем М=5 і природним порядком лічби

1. За потрібною кількістю розрядів n = 3 у перемикальній таблиці (рис. 9.5,а) заповнюємо колонки початкового Qі та наступного за надходженням лічильного імпульсу Qі+ станів тригерів з урахуванням того, що коди N = 5 ... 7 є надлишкові.

2. Вибираємо тип тригерів (для прикладу розглянемо варіанти лічильника на JK-, D- i TE-тригерах) та заповнюємо стовпці таблиці для функцій збудження на їх інформаційних входах. Так, JK-тригерові старшого розряду колонкам Q2Q2+ лівої частини таблиці відповідають колонки J2K2 її правої частини. Тому для переходів Q2Q2+ = 00, 01, 10 вносимо значення J2K2 = 0Х, 1Х, Х1, відтак аналогічно заповнюємо колонки для всіх інших розрядів згідно з таблицею переходів JK-тригера. Для розрядів на D-три- герах вносимо значення Dі = Qі+, а для ТЕ-тригерів занотовуємо Еі = 0, якщо тригер не перемикається та Еі = 1, якщо перемикається.

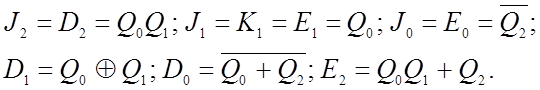

3. Безпосередньо з таблиці довизначенням Х = 1 маємо К2 = К0 = 1, а інші функції збудження мінімізуємо за діаграмами термів (на рис. 9.5,б порожнім клітинкам відповідають факультативні значення Х):

4. З’єднуючи синхровходи тригерів зі спільним лічильним входом С, а інші входи – згідно з функціями збудження, отримуємо варіанти реалізації лічильника на JK-, D- i TE-тригерах (рис. 9.5,в,г,д, відповідно). Такі лічильники є синхронні, отже, перемикаються без проміжних станів вихідного коду (див. рис. 9.4).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.