Аналогично не описывается

моделью константных неисправностей повреждение типа «замыкание» транзистора.

Рассмотрим такое повреждение транзистора V1 в схеме (рис. 4.4). На входном наборе ab = 10 получаем состояние схемы: V1 замкнут, V2 и V3 открыты.

В результате создается короткая цепь между питающими полюсами схемы и возникает

большой ток (показан стрелкой). Этот ток ( ![]() -ток)

по величине в несколько раз больше чем нормальный ток покоя КМОП-схемы. Измеряя

ток, можно обнаруживать данную неисправность.

-ток)

по величине в несколько раз больше чем нормальный ток покоя КМОП-схемы. Измеряя

ток, можно обнаруживать данную неисправность. ![]() -тестирование

позволяет обнаруживать многие виды неисправностей в КМОП-схемах, которые не

покрываются моделью константных неисправностей.

-тестирование

позволяет обнаруживать многие виды неисправностей в КМОП-схемах, которые не

покрываются моделью константных неисправностей.

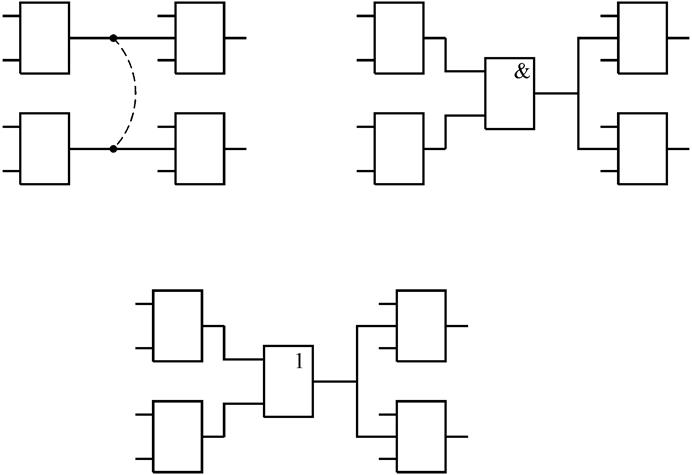

Отметим еще два вида распространенных неисправностей, не являющихся константными. Большую долю повреждений в современных микроэлектронных схемах с высокой степенью интеграции составляют короткие замыкания между линиями схемы (рис. 4.5, а) или мостиковые неисправности (bridging fault).

Рис.4.5. Моделирование короткого замыкания

При изготовлении печатных плат и интегральных схем их доля может составить 50–60%. Эти неисправности изменяют логическую функцию, реализуемую схемой. Логическое моделирование короткого замыкания линий осуществляется с помощью элемента И (рис. 4.5, б), если сигнал «логический 0» доминирует в схеме над сигналом «логическая 1», или с помощью элемента ИЛИ (рис. 4.5, в) в противном случае. Вопросы обнаружения коротких замыканий рассмотрены в разделе 4.4.

Важной областью тестирования является в настоящее время обнаружение временных неисправностей. Это связано с тем, что с увеличением быстродействия время переключения транзисторных схем становится соизмеримым с временем распространения электрических сигналов в монтажных проводах и дорожках печатных плат. Поэтому временные отклонения с большой вероятностью могут нарушать правильную работу логических схем. Рассматриваются две модели временных задержек (delay fault) – это задержки элемента (gate delay fault) и задержки пути (path delay fault). Методам их обнаружения посвящен раздел 4.6.

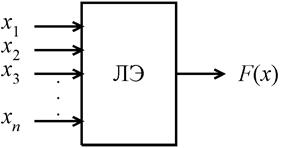

4.2. Тесты логических элементов

Логический элемент (ЛЭ)

представляет собой устройство (рис. 4.6), имеющее ![]() входов

и один выход, на котором реализуется некоторая функция алгебры логики

входов

и один выход, на котором реализуется некоторая функция алгебры логики ![]() .

.

Рис.4.6. Логический элемент

Дефект внутренней структуры элемента

приводит к тому, что на его выходе вместо функции ![]() реализуется

функция неисправности

реализуется

функция неисправности ![]() . Тест проверки ЛЭ должен

определить, какую из функций [

. Тест проверки ЛЭ должен

определить, какую из функций [![]() или

или ![]() ] реализует элемент. Число и вид функций

неисправности определяется внутренней структурой ЛЭ. Анализ неисправностей и

построение теста ЛЭ выполняют при помощи ТФН.

] реализует элемент. Число и вид функций

неисправности определяется внутренней структурой ЛЭ. Анализ неисправностей и

построение теста ЛЭ выполняют при помощи ТФН.

Рассмотрим процесс

построения теста на примере ЛЭ на транзисторе, реализующего функцию ИЛИ-НЕ

(рис. 4.3). Структура элемента содержит резисторы ![]() и

транзистор V. Рассмотрим обрывы резисторов

(короткие замыкания резисторов маловероятны), обрыв и короткое замыкание

перехода эмиттер–коллектор (Э–К) транзистора (обрывы и короткие замыкания

переходов эмиттер–база и база–коллектор в конечном счете приводят к указанным

неисправностям перехода Э–К). Рассмотрим только одиночные повреждения деталей,

хотя в данном случае тест, построенный для одиночных повреждений, будет

обнаруживать и любую их совокупность. К одиночным повреждениям (неисправностям)

относятся:

и

транзистор V. Рассмотрим обрывы резисторов

(короткие замыкания резисторов маловероятны), обрыв и короткое замыкание

перехода эмиттер–коллектор (Э–К) транзистора (обрывы и короткие замыкания

переходов эмиттер–база и база–коллектор в конечном счете приводят к указанным

неисправностям перехода Э–К). Рассмотрим только одиночные повреждения деталей,

хотя в данном случае тест, построенный для одиночных повреждений, будет

обнаруживать и любую их совокупность. К одиночным повреждениям (неисправностям)

относятся: ![]() – соответственно обрывы резисторов

– соответственно обрывы резисторов ![]() ;

; ![]() –

короткое замыкание перехода Э–К транзистора;

–

короткое замыкание перехода Э–К транзистора; ![]() – обрыв

перехода Э–К транзистора;

– обрыв

перехода Э–К транзистора; ![]() – соответственно обрывы

базы, эмиттера, коллектора транзистора.

– соответственно обрывы

базы, эмиттера, коллектора транзистора.

В табл. 4.1 представлена ТФН для рассматриваемого элемента.

|

№ |

Входной набор |

F |

Функции неисправности |

||||||||

|

|

|

|

|

|

|

|

|

|

|||

При внесенной неисправности |

|||||||||||

|

a b |

|

|

|

|

|

|

|

|

|

||

|

0 |

0 0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

2 |

1 0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

3 |

1 1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.