К достоинствам

МДП ключевых схем относится практическое отсутствие входного тока (тока

затвора) схемы – нагрузки (за исключением тока заряда паразитной ёмкости). Это

определяет высокий коэффициент разветвления ![]() (нагрузочную

способность) МДП логических схем. Во многих применениях существенно, что МДП

транзисторы как униполярные обладают высокой устойчивостью к радиационному

воздействию. Отметим также малую зависимость параметров МДП транзисторов от

температуры. Теоретически определён режим МДП транзистора (критический ток),

когда температурная зависимость вовсе отсутствует.

(нагрузочную

способность) МДП логических схем. Во многих применениях существенно, что МДП

транзисторы как униполярные обладают высокой устойчивостью к радиационному

воздействию. Отметим также малую зависимость параметров МДП транзисторов от

температуры. Теоретически определён режим МДП транзистора (критический ток),

когда температурная зависимость вовсе отсутствует.

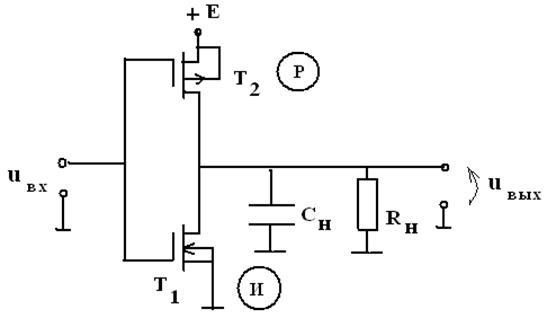

3.6.2. Базовый элемент КМДП – логических схем. Таким элементом является инвертор, использующий два МДП - транзистора с противоположным (дополняющим, комплементарным) типом проводимости (рис.3.20)

Рис.3.20

При напряжении на

входе ![]() напряжение затвор – исток транзистора

напряжение затвор – исток транзистора ![]() с проводимостью

с проводимостью ![]() типа

равно нулю и согласно рис.3.19 транзистор

типа

равно нулю и согласно рис.3.19 транзистор ![]() закрыт. Положительное

напряжение

закрыт. Положительное

напряжение ![]() на затворе транзистора

на затворе транзистора ![]() открывает его. После разряда паразитной

ёмкости

открывает его. После разряда паразитной

ёмкости ![]() (см.рис.3.20) выходное напряжение равно нулю.

(см.рис.3.20) выходное напряжение равно нулю.

При нулевом

напряжении на входе открывается транзистор ![]() типа (

типа (![]() ) и закрывается

) и закрывается ![]() .

После заряда ёмкости нагрузки напряжение на выходе близко к напряжению питания

и ток в канале не протекает, т.к. сопротивление нагрузки составляет сотни Мом. Если

используются условия

.

После заряда ёмкости нагрузки напряжение на выходе близко к напряжению питания

и ток в канале не протекает, т.к. сопротивление нагрузки составляет сотни Мом. Если

используются условия ![]()

![]() , то в

процессе переключения напряжение закрытия

, то в

процессе переключения напряжение закрытия ![]() и напряжение

открытия

и напряжение

открытия ![]() достигаются одновременно, поэтому импульс

«сквозного» тока от источника питания не возникает.

достигаются одновременно, поэтому импульс

«сквозного» тока от источника питания не возникает.

На рис.3.21 показана

схема, выполняющая логическую операцию И-НЕ с использованием комплементарных

МДП транзисторов. Если хотя бы один из транзисторов ![]() в

последовательной цепочке закрыт, соответствующий транзистор в параллельной цепочке

в

последовательной цепочке закрыт, соответствующий транзистор в параллельной цепочке

![]() , как было показано на схеме инвертора

рис.3.20, открыт и на выходе схемы логическая единица.

, как было показано на схеме инвертора

рис.3.20, открыт и на выходе схемы логическая единица.

Рис.3.21

Только в случае, когда открыты

оба транзистора ![]() (

(![]() ), закрыты

транзисторы

), закрыты

транзисторы ![]() и

и ![]() и на

выходе имеется напряжение логического нуля.

и на

выходе имеется напряжение логического нуля.

Не трудно построить схему, на которой взаимно изменены последовательное и параллельное соединение транзисторов. Ясно, что такая схема будет выполнять логическую операцию ИЛИ-НЕ. В обеих схемах без труда осуществляется расширение числа входов.

3.6.4. Краткие сведения о технических показателях ИЛС на МДП транзисторах. В таблице 3 приведены технические показатели некоторых микросхем ИЛС на КМДП транзисторах. Из таблицы видно, что прогресс микроэлектронной технологии в отношении уменьшения времени задержки прямо связан с уменьшением энергии переключения, что определяется уменьшением размеров элементов схемы и напряжения питания. В таблице 3 приведены также оценочные значения мощности потребления микросхем, которые должны снижаться с уменьшением энергии переключения, но в силу малого уровня потребления приняты одинаковыми.

В заключение отметим, что повышение быстродействия интегральных микросхем возможно с применением новых материалов и технологий. Среди них назовём арсенид-галлиевые схемы, выпускаемые в составе серии К6500, со временем задержки 0,1-0,4 нс, энергией переключения 0,3-0,6 пДж и потребляемой мощностью 0,3-0,6 мВт на вентиль.

Новейшая технология, разработанная по заказу корпорации IBM (США), использует германиево-кремниевую технологию, при этом достигаются граничные частоты транзисторов в 50-100 ГГц, что соответствует временам задержки около20-30 пс. Потребляемая мощность около 100 мВт на вентиль ограничивает пропорциональное увеличение плотности компоновки интегральных схем.

Таблица 3 Технические показатели КМОП ИЛС

|

Серия |

Потребляемая мощность, мкВт/МГц |

Время задержки, нс |

Энергия переключения, пДж |

Коэффициент разветвления, п |

|

К561 |

2,5 |

45-200 |

0,1 |

50 |

|

564 |

2,5 |

45-200 |

0,1 |

50 |

|

1564 |

2,5 |

10-45 |

0,025 |

50 |

|

КР1554 |

2,5 |

3,5-17 |

0,008 |

50 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.