Из словесного описания работы

мультиплексора можно заключить, что базовый мультиплексор имеет два входа для

цифровых каналов (![]() ). Поскольку по определению управление цифровое, то для нумерации двух

каналов достаточно одноразрядных двоичных чисел. Следовательно, у

мультиплексора на два канала добавляется еще один вход управления ( А0 ), на нем выставляется номер (адрес) канала, который

должен быть подключен к выходу. Поскольку каналы D0 и D1 и вход управления А0

цифровые и представляют собой аргументы логической функции мультиплексора F, то мы можем составить таблицу

истинности. При этом для А0=0 записываем в колонку для F цифровые сигналы D0 , а для А0 = 1 –

цифровые сигналы D1. Записав СДНФ и оптимизировав ее с

помощью карты Карно, мы получим логическую формулу для базового мультиплексора

2-1 (два в один). Отметим, что в этом, самом простом, случае таблица истинности

содержит 23 = 8 строк. Попытка использовать этот прямой путь

составления таблицы истинности уже для мультиплексора 4-1 приводит к таблице

истинности в 26 = 64 строки, а для мультиплексора 8-1 в 211 =

2048 строк! Отчего так катастрофически нарастает сложность? Почти очевидно, это

происходит из-за того, что, действуя как обычно, мы вынуждены выписывать все

возможные комбинации сигналов каналов. При таком подходе получается, что при

составлении таблицы истинности мы рассматриваем мультиплексор как переключатель

данных определенных каналов. На самом деле, по определению мультиплексор должен

переключать "позиции", на которые поступают цифровые данные. Отсюда следует,

что при составлении таблицы истинности мультиплексоров аргументами надо считать

каналы (позиции) и адреса каналов, а функция F =1 приобретает смысл функции подключения заданного

канала.

). Поскольку по определению управление цифровое, то для нумерации двух

каналов достаточно одноразрядных двоичных чисел. Следовательно, у

мультиплексора на два канала добавляется еще один вход управления ( А0 ), на нем выставляется номер (адрес) канала, который

должен быть подключен к выходу. Поскольку каналы D0 и D1 и вход управления А0

цифровые и представляют собой аргументы логической функции мультиплексора F, то мы можем составить таблицу

истинности. При этом для А0=0 записываем в колонку для F цифровые сигналы D0 , а для А0 = 1 –

цифровые сигналы D1. Записав СДНФ и оптимизировав ее с

помощью карты Карно, мы получим логическую формулу для базового мультиплексора

2-1 (два в один). Отметим, что в этом, самом простом, случае таблица истинности

содержит 23 = 8 строк. Попытка использовать этот прямой путь

составления таблицы истинности уже для мультиплексора 4-1 приводит к таблице

истинности в 26 = 64 строки, а для мультиплексора 8-1 в 211 =

2048 строк! Отчего так катастрофически нарастает сложность? Почти очевидно, это

происходит из-за того, что, действуя как обычно, мы вынуждены выписывать все

возможные комбинации сигналов каналов. При таком подходе получается, что при

составлении таблицы истинности мы рассматриваем мультиплексор как переключатель

данных определенных каналов. На самом деле, по определению мультиплексор должен

переключать "позиции", на которые поступают цифровые данные. Отсюда следует,

что при составлении таблицы истинности мультиплексоров аргументами надо считать

каналы (позиции) и адреса каналов, а функция F =1 приобретает смысл функции подключения заданного

канала.

Учтем приведенные замечания и составим таблицу истинности базового мультиплексора 2-1, приняв за аргументы логической функции включения каналов F, адреса A и каналы D0 и D1 (Табл. 1).

Таблица 3.1.

|

А |

D |

F |

|

0 |

D0 |

1 |

|

1 |

D1 |

1 |

По таблице запишем ФАЛ по единицам

![]()

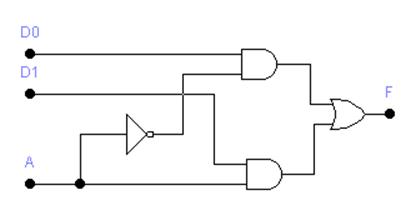

по которой сразу нарисуем логическую схему мультиплексора 2-1 на элементах И, ИЛИ, НЕ (рис. 3.1).

Рис. 3.1. Логическая схема мультиплексора 2-1.

Составим логическую схему мультиплексора 4-1. Чтобы занумеровать четыре канала (D0, D1, D2, D3 ) надо два двоичных разряда А0 и А1. Заполненная таблица истинности приведена в табл. 3.2.

Таблица 3.2

|

A1 |

A0 |

D |

F |

|

0 |

0 |

D0 |

1 |

|

0 |

1 |

D1 |

1 |

|

1 |

0 |

D2 |

1 |

|

1 |

1 |

D3 |

1 |

По заполненной таблице запишем ФАЛ MUX 4-1 по единицам

![]()

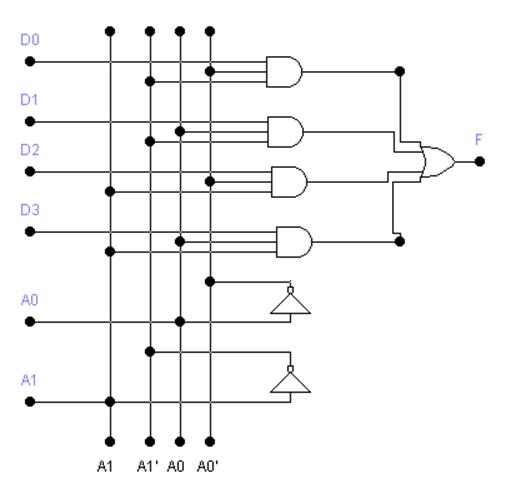

и нарисуем логическую схему в базисе НЕ, И, ИЛИ (рис. 3.2).

Рис. 3.2. Логическая схема MUX 4-1 на элементах И, ИЛИ, НЕ.

1.2. Наращивание размерности мультиплексоров

Типичные выпускаемые серийно мультиплексоры имеют 2. 4, 8 или 16 входных каналов. Рассмотрим принцип наращивания размерности каналов на основе использования мультиплексоров меньшей размерности. Построим мультиплексор 4-1 из мультиплексоров 2-1. Можно преобразовать ФАЛ (3.2) мультиплексора 4-1 к следующему виду

![]()

![]()

![]() (3.3)

(3.3)

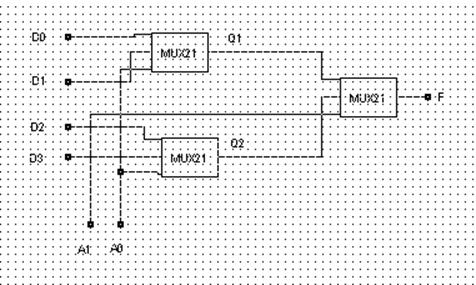

По структуре формулы нельзя не увидеть, что мультиплексор 4-1 можно построить из двух мультиплексоров 2-1 Q0 и Q1, соединив их адресные входы в один - A0 , а выходы подать на третий мультиплексор 2-1, адресный вход которого представляет второй разряд адресного входа мультиплексора 4-1 – А1. На рис. 3.3 изображена логическая схема мультиплексора 4-1, составленная из трех мультиплексоров 2-1.

Рис. 3.3. Мультиплексор 4-1, собранный из мультиплексоров 2-1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.