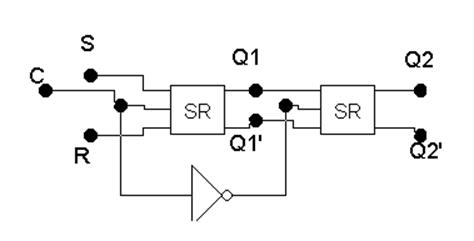

Синхронные SR-триггеры имеют дополнительный С-вход для подачи синхронизирующих импульсов, которые управляют подачей информационных сигналов на триггер (рис. 4.1, б). В подобных синхронных триггерах схемы оказываются прозрачны на время действия синхроимпульса для всех помех. Одним из типовых способов устранения этого недостатка является построение двухступенчатых синхронных триггеров по схеме ведущий—ведомый. Такой триггер строится на двух триггерах – один называется ведущим, другой ведомым. Занесение информации в триггеры разнесено во времени: вначале информация записывается в первый триггер, а затем во второй. Это достигается включением инвертора в цепь синхронизации (рис. 4.2).

Рис. 4.2. Схема двухступенчатого синхронного SR-триггера с инвертором

1.2. JK - триггеры. Неопределенные состояния в SR-триггерах при S = R = 1 можно исключить, если придать смысл переходам состояний при данных сигналах. Этот смысл нашли в том, что чтобы при S = R = 1 SR-триггер переключался в состояния, противоположные исходным. Теперь можно дать функциональное определение для JK-триггера. Элемент памяти JK-триггер хранит единицу до сброса ( K ), а нуль – до установки единицы ( J ). В определении подразумевается эквивалентность входов S , J и R, K. Тогда, проставив в таблице переходов состояний SR-триггера на неопределенных состояниях 1 и 0, получим таблицу переходов состояний для JK-триггера (см. табл. 4.1). Словарь переходов триггеров, как мы знаем, строится по таблице переходов состояний и словарь переходов JK-триггера представлен в табл. 4.3:

Табл.4.3.

|

QàQ* |

J |

K |

|

0 à 0 |

0 |

- |

|

0 à 1 |

1 |

- |

|

1 à 0 |

- |

1 |

|

1 à 1 |

- |

0 |

Схему JK-триггера можно построить, используя SR-триггеры. Это значит, что состояния SR-триггера должны управляться пока неизвестной комбинационной схемой так, чтобы получилась таблица переходов JK-триггера. Следовательно, аргументами у искомой комбинационной схемы будут выступать исходные состояния Q, переходы QàQ* и входы J и K, а выходы – управляющие входы SR-триггера S и R. Значения S и R для каждого перехода определяются словарем переходов SR-триггера (табл. 4.2). Эти исходные данные и результат заполнения столбцов S и R представлены так называемой таблицей возбуждения памяти SR-триггера в табл. 4.4.

Табл.4.4.

|

QàQ* |

J |

K |

S |

R |

|

0 à 0 |

0 |

- |

0 |

- |

|

0 à 1 |

1 |

- |

1 |

0 |

|

1 à 0 |

- |

1 |

0 |

1 |

|

1 à 1 |

- |

0 |

- |

0 |

Записывая логические формулы для S и R по единицам, получим уравнения связи между управляющими входами SR-триггера и JK-триггера:

![]()

которые легко реализуются комбинационными элементами. На рис. 4.3 изображена схема JK-триггера, образованная на основе SR-триггера.

Рис. 4.3 Структурная схема JK-триггера

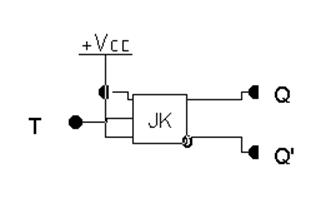

1.3. T – триггеры. Для счета в одном разряде двоичной системы счисления достаточно иметь элемент памяти с двумя состояниями (0, 1), управляемыми цифровыми сигналами так, чтобы счетный сигнал переключал исходное состояние на противоположное. Элемент памяти T-триггер хранит единицу или нуль до поступления следующего счетного импульса. Т-триггер образуется из JK-триггера введением нового входа Т = J = K = 1. У JK-триггеров со входом синхронизации С удобно принять за счетный вход С = Т, а вход J = K — за управляющий.

Рис. 4.4. Структурная схема Т-триггера

Таблица истинности переходов состояний и словарь переходов составляются элементарно исходя из функционального назначения Т-триггера, они представлены в табл. 4.5 и 4.6.

Табл. 4.5 Табл. 4.6

|

Q |

T |

Q* |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

|

QàQ* |

T |

|

0 à 0 |

0 |

|

0 à 1 |

1 |

|

1 à 0 |

1 |

|

1 à 1 |

0 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.