Данная в табл, 5.1 позиционная запись двоичных чисел имеет следующие закономерности. В младшем разряде Q0 нули и единицы чередуются как 0101… , что естественно, так как при прямом счете мы должны прибавлять единицу к младшему разряду. В следующем разряде нули и единицы чередуются парами как 00110011, в третьем разряде – четверками. При этом переключения в следующих разрядах при прямом счете происходят тогда, когда предыдущий разряд изменяется в направлении 1-0. Для обратного счета мы должны рассматривать табл, 5.1 в обратном порядке от столбца 7. В этом случае переключения в следующих разрядах происходят тогда, когда предыдущий разряд изменяется в направлении 0-1.

Отмеченные закономерности позиционной записи двоичных чисел позволяют синтезировать схемы многоразрядных двоичных счетчиков для прямого и обратного счета импульсов. Мы уже располагаем устройством – Т-триггером, который реализует счет в одном двоичном разряде, его состояния отождествим со строкой Q0. Для следующих разрядов табл. 5.1 возьмем еще два Т-триггера, состояния которых соотнесем со строками Q1, Q2. Теперь учтем, что единицы физически представляются импульсами. Тогда становится очевидным, что для прямого счета Т-триггеры должны запускаться задним фронтом импульса, а для обратного счета – передним.

Сформулируем выводы. Многоразрядные двоичные счетчики прямого и обратного счета могут быть построены в виде последовательного соединения одноразрядных Т-триггеров. При этом запуск Т-триггеров по переднему или заднему фронту определяет тип счетчика как суммирующего или вычитающего.

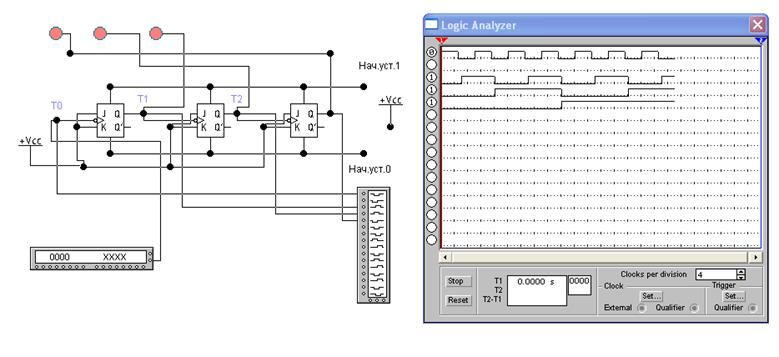

На рис. 5.1 показана схема трехразрядного двоичного суммирующего счетчика на Т-триггерах с динамическим управлением по заднему фронту. Т-триггеры в приведенной схеме представляют собой JK-триггеры в счетном режиме, которые реализуются подачей на управляющие входы J и K высокого уровня – логической единицы. На вход Т-триггера младшего разряда с генератора кодовых слов подаются счетные импульсы, выходные сигналы счетчика – состояния триггеров отображаются светодиодными индикаторами и временными диаграммами состояний на логическом анализаторе.

Рис. 5.1. Структурная схема и временные диаграммы работы асинхронного трехразрядного двоичного счетчика на основе Т-триггеров с динамическим управлением по заднему фронту.

С помощью временных диаграмм легко показать, что если в схеме рис. 5.1 переключить выходы триггеров на инверсные (или использовать Т-триггеры с динамическим запуском передним фронтом), то получится вычитающий счетчик. Таким образом, на триггерах с динамическим запуском или передним или задним фронтом переключением прямых выходов на обратные можно построить как суммирующие, так и вычитающие счетчики. Это свойство используется при построении схем реверсивных счетчиков с помощью переключателей выходов триггеров.

Счетчики, построенные по принципу последовательного (а не одновременного) запуска триггеров, называются асинхронными счетчиками. Такие счетчики имеют наименьшее количество компонентов, чем счетчики любого другого типа. Но они обладают наименьшим быстродействием из-за того, что задержки распространения всех триггеров схемы суммируются. Каждый триггер запускается предыдущим и должен ждать установления запускающего фронта импульса от предыдущего триггера. Этот недостаток устраняется подачей каждого счетного импульса одновременно (синхронно) на все триггеры. Какие триггеры перейдут в противоположное состояние определяется комбинационной логикой, подключаемой к входам разрешения запуска Т-триггеров. Входом разрешения у JK-триггеров в счетном режиме являются вывод соединенных J и K входов. Счетчики, построенные по принципу одновременного запуска триггеров счетными импульсами, называются синхронными счетчиками. Реализация комбинационной логики разрешения оказывается очень простой, если учесть принцип работы счетчиков, который диктуется опять-таки позиционной записью чисел (см. табл. 5.1): любой из триггеров может переключиться тогда и только тогда, когда выходные сигналы равны 1 во всех разрядах младше данного. По этому принципу можно построить схемы разрешения двумя способами: с последовательной передачей сигналов разрешения от младшего разряда к старшему и с параллельной – для всех разрядов одновременно.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.