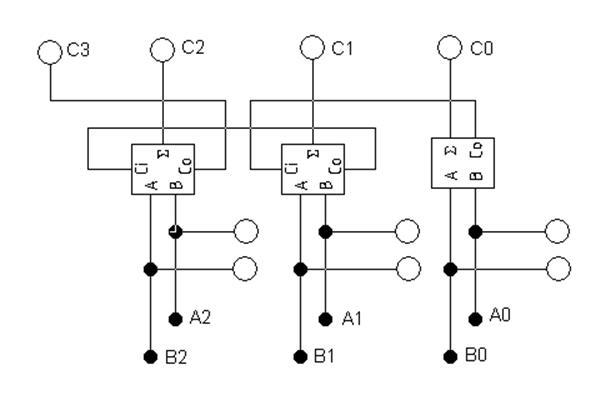

На рис. 2.3 показана логическая схема трехразрядного параллельного сумматора, построенная на сумматорах из библиотеки EWB. Для проверки работоспособности сумматора подключены пробники — светодиодные лампочки. Слагаемые – трехразрядные двоичные числа — А2А1А0 и В2В1В0 параллельно подаются на входы сумматоров; сумма – С3С2С1С0 формируется на выходах каждого разряда. На будущее обратите внимание, что структурно схема составлена так, как идут разряды при записи чисел – справа налево, а не так, как мы пишем или читаем — слева направо.

Рис. 2.3. Логическая схема трехразрядного параллельного сумматора

2. Порядок выполнения работы

1. Начертить логическую схему полусумматора в EWB (Рис.2.1,а) подключить ее к логическому преобразователю и по таблице истинности убедиться в правильности работы схемы. То же самое проделать с логической схемой полусумматора по схеме рис.2.1,б.

2. Самостоятельно получить логическую формулу и логическую схему полусумматора в базисе И—НЕ и проверить правильность ее работы с помощью логического преобразователя.

3. Начертить логическую схему полного сумматора в EWB (Рис.2.2,а) подключить его входы к генератору кодовых слов и к логическому анализатору; выходы сумматора подключить тоже к отдельным клеммам логического анализатора; на генераторе кодовых слов набрать аргументы (входные сигналы) таблицы истинности сумматора: А, В, P0 по порядку и, запустив схему, получить на логическом анализаторе осциллограммы таблицы истинности полного сумматора. Убедиться в правильности работы схемы.

4. Начертить логическую схему параллельного трехразрядного сумматора (рис.2.3); самостоятельно выбрать и реализовать на схеме вариант подачи трехразрядных чисел на входы сумматоров (от генератора кодовых слов или с помощью источника постоянного напряжения 5V и элемента заземления).

Протестировать схему.

3. Содержание отчета

1.Цели работы.

2.Логические схемы, таблица истинности и логические формулы полусумматора.

3.Логические схемы, таблица истинности и логические формулы полного сумматора.

4. Логическая схема трехразрядного сумматора с тестовыми приборами.

5. Личные выводы по работе: что нового для себя узнали, что научились делать.

Контрольные вопросы

1. Чем отличаются друг от друга сумматоры по модулю два, полусумматоры и полные сумматоры?

2. Воспроизведите (на память) процедуры синтеза логических схем полусумматора и полного сумматора.

3. Как осуществляется переход от таблицы истинности к логической формуле и далее к логической схеме в желаемом базисе?

4. Из каких соображений делается выбор для представления таблицы истинности логическими формулами в виде СДНФ и СКНФ?

5. Какие способы минимизации логических функций использованы в данной работе?

6. Какие машинные коды используются в компьютерах для представления чисел?

7. Как с помощью сумматора вычислить разность двух чисел?

Лабораторная работа № 3

Мультиплексоры и демультиплексоры

Цели работы. Изучение принципов построения схем мультиплексоров и демультиплексоров и ознакомление с их применениями. Исследование схем мультиплексоров и демультиплексоров в виртуальной электронной лаборатории EWB.

1. Мультиплексоры (селекторы данных)

1.1.Построение логических схем мультиплексоров.

Мультиплексоры ( MUX ) – это комбинационное устройства, которые выполняют функции многопозиционных переключателей цифровых каналов и работают под цифровым управлением. Другими словами, мультиплексор выбирает один из нескольких цифровых каналов и подключает его на один выход. Этот процесс называется мультиплексированием. Построим логическую схему базового мультиплексора с двумя входами (каналами данных) исходя из его функционального назначения.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.