Table 4.9 Управляющие сигналы, вычисляемые заранее в течении этапа ID для каждого из 10 выполняющихся состояний. Сигналы в первой таблице типа x, то есть, они управляют только этапом EX.

|

EX |

ALUDdoe |

SHDdoe |

linkDdoe |

add |

test |

Rtype |

|||||

|

M |

|||||||||||

|

WB |

|||||||||||

|

shift |

1 |

1 |

|||||||||

|

shiftl |

1 |

1 |

|||||||||

|

alu |

1 |

1 |

|||||||||

|

aluI |

1 |

||||||||||

|

test |

1 |

1 |

1 |

||||||||

|

testI |

1 |

1 |

|||||||||

|

addrL |

1 |

1 |

|||||||||

|

addrS |

1 |

1 |

|||||||||

|

savePC |

1 |

||||||||||

|

noEX |

|||||||||||

|

EX |

MARce |

bmuxsel |

MDRwce amuxsel shift4s |

Cad3ce |

|||||||

|

M |

Dmw |

Cad4ce Cce |

Dmr MDRrce |

||||||||

|

WB |

GPRw |

shift41 |

|||||||||

|

Type |

x |

x |

y |

z |

z |

||||||

|

shift |

1 |

1 |

|||||||||

|

shiftl |

1 |

||||||||||

|

alu |

1 |

1 |

|||||||||

|

alul |

1 |

||||||||||

|

test |

1 |

1 |

|||||||||

|

testl |

1 |

1 |

|||||||||

|

addrL |

1 |

1 |

1 |

||||||||

|

addrS |

1 |

1 |

|||||||||

|

savePC |

1 |

1 |

|||||||||

|

noEX |

|||||||||||

|

|

|

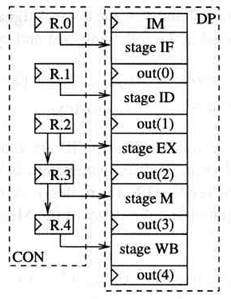

Рисунок 4.9 Буферизация вычисляемых заранее управляющих сигналов |

Рисунок 4.10 Структура путей данных DP и вычисляемого заранее управления CON машины DLXσ

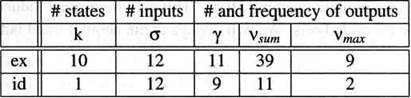

Таблица 4.10 Параметры двух управляющих автоматов; один вычисляет заранее сигналы Мура (ex) а другой генерирует сигналы Mealy (id).

|

Коэф. объединения по входу состояний |

# и длина одночленов |

||||

|

fansum |

fanmax: |

#M |

lsum |

lmax |

|

|

ex |

15 |

3 |

15 |

104 |

11 |

|

id |

- |

- |

5 |

22 |

10 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.